# Qualcomm Technologies International, Ltd.

#### **CSRB31024 A06 LGA Automotive**

Production Information Data Sheet 80-CU051-1 Rev. AE November 9, 2018

#### **Device description**

- Bluetooth<sup>®</sup> low energy technology single-mode SoC

- Supported by Qualcomm<sup>®</sup> Bluetooth<sup>®</sup> Low Energy toolset and applications

- 16-bit RISC MCU, 256 KB internal SPI flash, 80 KB RAM,

192 KB ROM, 60 KB OTP

- 15 digital PIO, 1 analog AIO, SPI, I<sup>2</sup>C, quadrature decoders, LED PWM module, key scanner, 10-bit auxiliary ADC

- Ultra low-power Bluetooth low energy technology radio

Bluetooth v5.0 specification compliant radio

- 36-lead 5 x 5 x 0.75 mm, 0.5 mm pitch LGA

- AEC-Q100 Automotive Grade 3 qualified

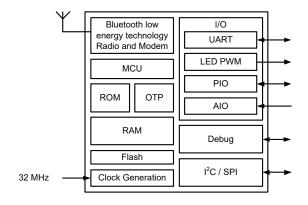

#### System architecture

#### **Applications**

- Bluetooth low energy technology:

- Keyless entry system/car share

- Infotainment remote control

- Wireless charging controller

- Gate/garage remote control

- Driver health monitor

- Driver comfort and convenience sensor/control

- Qualcomm<sup>®</sup> Mesh connectivity: Internet of Things control

#### Confidential and Proprietary – Qualcomm Technologies International, Ltd.

NO PUBLIC DISCLOSURE PERMITTED: Please report postings of this document on public servers or websites to DocCtrlAgent@qualcomm.com.

**Restricted Distribution:** Not to be distributed to anyone who is not an employee of either Qualcomm Technologies International, Ltd. or its affiliated companies without the express approval of Qualcomm Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others without the express written permission of Qualcomm Technologies International, Ltd.

All Qualcomm products mentioned herein are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

Qualcomm and Qualcomm are trademarks of Qualcomm Incorporated, registered in the United States and other countries. Other product and brand names may be trademarks or registered trademarks of their respective owners.

This technical data may be subject to U.S. and international export, re-export, or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

Qualcomm Technologies International, Ltd. (formerly known as Cambridge Silicon Radio Limited) is a company registered in England and Wales with a registered office at: Churchill House, Cambridge Business Park, Cowley Road, Cambridge, CB4 0WZ, United Kingdom.

Registered Number: 3665875 | VAT number: GB787433096

# General description

CSRB31024 LGA is Qualcomm Technologies International, Ltd. (QTIL)'s latest generation automotive-qualified Bluetooth low energy technology single-mode platform device with ultra low power consumption.

Qualcomm Bluetooth Low Energy technology enables ultra low-power connectivity and basic data transfer for applications previously limited by the power consumption, size constraints, and complexity of other wireless standards. The Qualcomm Bluetooth Low Energy platform provides everything required to create a Bluetooth low energy technology product with RF, baseband, MCU, qualified Bluetooth v5.0 specification stack, and customer application running on a single IC.

Bluetooth low energy technology enables connectivity and data transfer to leading smartphone, tablet, and personal computing devices including iOS, Android, Windows Phone 8, and Blackberry OS10 devices.

Qualcomm Mesh places the smartphone at the center of the Internet of Things enabling an almost unlimited number of Bluetooth low energy technology enabled devices to be simply networked together and controlled directly from a single smartphone, tablet, or PC.

CSRB31024 LGA supports profiles for advanced remote controls and custom profiles (such as keyless entry and automotive switch pack).

# Device details

#### Ultra low-power Bluetooth low energy technology radio

- Single pin RF connection (50 Ω impedance in Tx and Rx modes)

- Requires no external RF components<sup>a</sup>

- Operates from a single crystal

- Bluetooth v5.0 specification compliant

#### Bluetooth transmitter

- 4 dBm RF transmit power

- Tx power control

- No external power amplifier or Tx/Rx switch required

#### Bluetooth receiver

- -90.0 dBm sensitivity

- Rx Boost mode available: Enhances Rx sensitivity at higher receive current cost

- Receiver large input level saturation -5 dBm

- Integrated channel filters

- Digital demodulator for improved sensitivity and cochannel rejection

- Fast AGC for enhanced dynamic range

#### **Bluetooth stack**

QTIL protocol stack runs on the integrated MCU:

- Support for Bluetooth v5.0 specification features:

- Master and slave operation

- Including encryption

- Software stack in firmware includes:

- □ GAP

- □ L2CAP

- Security manager

- Generic attribute protocol

- Attribute profile

- Bluetooth low energy technology profile support

#### **Synthesizer**

Fully integrated synthesizer requires no external VCO varactor diode, resonator, or loop filter

#### Baseband and software

- Integrated MAC for all packet types enables packet handling without the need to involve the MCU

- <sup>a</sup> Certain antennas with gain may require a simple filter.

#### **Physical interfaces**

- 15 digital flexible PIO

- 1 analog AIO

- UART

- SPI interface

- Debug SPI interface for programming

- I<sup>2</sup>C controller

- 4 x quadrature decoders

- 5 x LED PWMs

- Keyboard scanner

- 10-bit auxiliary ADC

#### **Auxiliary features**

- Battery monitor

- 6 power modes

- Power management features include software shutdown and hardware wake-up

- Wake-up power management from any PIO

- Integrated switch-mode power supply

- Linear regulator (internal use only)

- AES-128

- Watchdog timer

#### Memory

- 256 KB internal flash

- 64 KB (Code) and 16 KB (Data) RAM

- 192 KB ROM

- 60 KB OTP

#### **Battery**

■ Battery input voltage 2.7 V to 3.3 V

#### **Temperature specification**

■ Operating temperature -40 to 85 °C

#### **Package**

- 36-lead 5 x 5 x 0.75 mm, 0.5 mm pitch LGA

- Single side routing pinout optimized

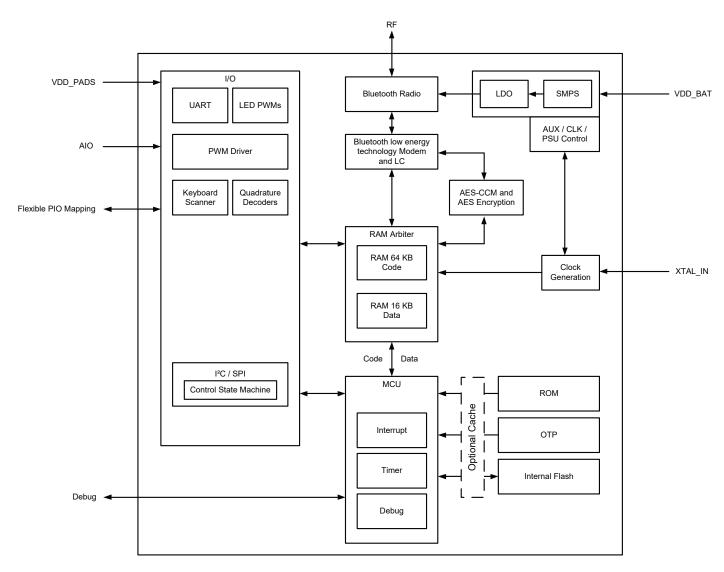

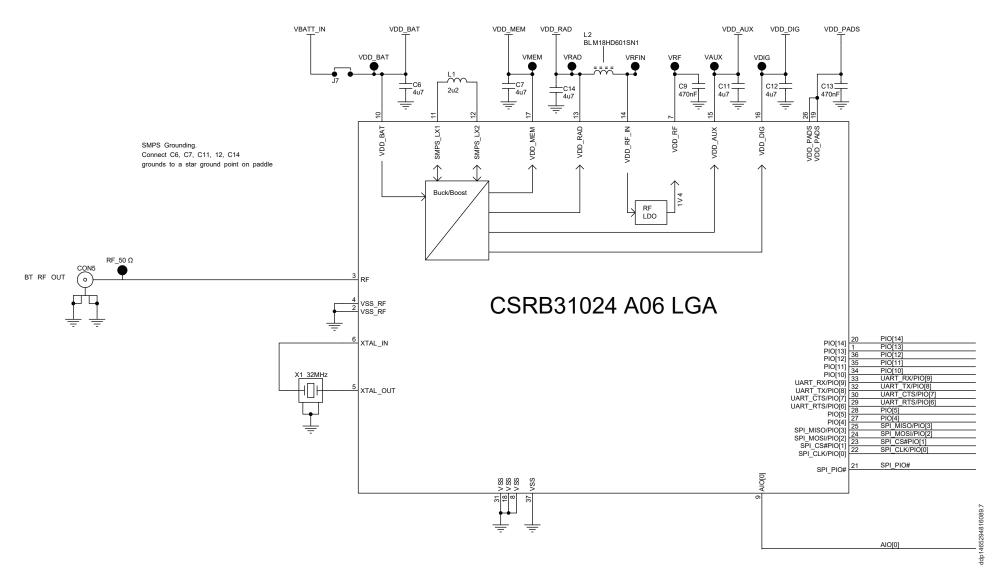

# CSRB31024 LGA functional block diagram

CSRB31024 LGA functional block diagram

# Ordering information

| Dovice        | Package                  |                                 |                 | Order number                    |

|---------------|--------------------------|---------------------------------|-----------------|---------------------------------|

| Device        | Type                     | Size                            | Shipment method | Order Humber                    |

| CSRB31024 LGA | LGA 36-lead<br>(Pb free) | 5 x 5 x 0.75 mm<br>0.5 mm pitch | Tape and reel   | CSR-B31024-0-36BLGA-<br>MT-00-0 |

#### NOTE

Your attention is drawn to QTIL's Terms of Supply, see <a href="http://www.qualcomm.com/salesterms">http://www.qualcomm.com/salesterms</a> or please request a copy), in particular the section covering Product Warranties and Disclaimers. Please note that the product warranty differs for production, pre-production, and other versions.

**Production** status minimum order quantity is 2 kpcs.

**Supply chain:** QTIL's manufacturing policy is to multisource volume products. For further details, contact your local sales account manager or representative.

## **QTIL** contacts

General information

Information on this product

Customer support for this product

Details of compliance and standards

Help with this document

http://www.qualcomm.com qcsales@qti.qualcomm.com http://www.csrsupport.com

http://createpoint.qti.qualcomm.com product.compliance@qti.qualcomm.com document.feedback@qti.qualcomm.com

# **Revision history**

| Revision | Date          | Change reason                                                |  |  |

|----------|---------------|--------------------------------------------------------------|--|--|

| 1        | February 2017 | Initial release. Alternative document number CS-00401212-DS. |  |  |

| AA       | June 2017     | Updated to Engineering Sample.                               |  |  |

| AB       | October 2017  | Updated to Pre-production Information.                       |  |  |

| AC       | November 2017 | Updated Operating Conditions.                                |  |  |

| AD       | February 2018 | Updated Operating Conditions.                                |  |  |

| AE       | November 2018 | Updated to Production Information.                           |  |  |

# Status information

QTIL Product Data Sheets progress according to the following formats: Advance Information, Engineering Sample, Pre-production Information, and Production Information. The status of this document is **Production Information**.

#### **Advance Information**

Information for designers concerning QTIL product in development. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

#### **Engineering Sample**

Information about initial devices. Devices are untested or partially tested prototypes, their status is described in an Engineering Sample Release Note. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All detailed specifications including pinouts and electrical specifications may be changed by QTIL without notice.

#### **Pre-production Information**

Pinout and mechanical dimension specifications finalized. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All electrical specifications may be changed by QTIL without notice.

#### **Production Information**

Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

Production Data Sheets supersede all previous document versions.

# **Device implementation**

As the feature-set of the CSRB31024 LGA is firmware build-specific, see the relevant software release note for the exact implementation of features on the CSRB31024 LGA.

# Life support policy and use in safety-critical applications

QTIL products are not authorized for use in life-support or safety-critical applications. Use in such applications is done at the sole discretion of the customer. QTIL will not warrant the use of its devices in such applications.

# **QTIL** environmental and RoHS compliance

CSRB31024 LGA devices meet the requirements of Directive 2011/65/EU of the European Parliament and of the Council on the Restriction of Hazardous Substance (RoHS).

CSRB31024 LGA devices are free from halogenated or antimony trioxide-based flame retardants and other hazardous chemicals. For more information, see QTIL *Environmental declaration statement for QTIL semiconductor products*.

# **Contents**

| General description                                          |

|--------------------------------------------------------------|

| Device details                                               |

| CSRB31024 LGA functional block diagram                       |

| Ordering information                                         |

| QTIL contacts                                                |

| Revision history                                             |

| Status information                                           |

| Device implementation                                        |

| Life support policy and use in safety-critical applications  |

| QTIL environmental and RoHS compliance                       |

| 1 Package information                                        |

| 1.1 Chip marking                                             |

| 1.2 CSRB31024 LGA pinout diagram                             |

| 1.3 Device terminal functions                                |

| 1.3.1 Device terminal functions (Radio)                      |

| 1.3.2 Device terminal functions (Synthesizer and oscillator) |

| 1.3.3 Device terminal functions (PIO port)                   |

| 1.3.4 Device terminal functions (Test and debug)             |

| 1.3.5 Device terminal functions (Power supplies and control) |

| 1.4 Package dimensions                                       |

| 1.5 PCB design and assembly considerations                   |

| 1.6 Typical solder reflow profile                            |

| 2 Bluetooth modem                                            |

| 2.1 RF port                                                  |

| 2.2 RF receiver                                              |

| 2.2.1 RSSI                                                   |

| 2.3 RF transmitter                                           |

| 2.3.1 Power amplifier                                        |

| 2.4 Bluetooth radio synthesizer                              |

| 2.5 Baseband                                                 |

| 2.5.1 Physical layer hardware engine                         |

| 3 Clock generation                                           |

| 3.1 Clock architecture                                       |

| 3.2 Crystal oscillator: XTAL_IN and XTAL_OUT                 |

| 3.2.1 Crystal specification                                                                   | <b>2</b> 4 |

|-----------------------------------------------------------------------------------------------|------------|

| 3.2.2 Crystal configuration                                                                   | 25         |

| 3.3 Sleep clock                                                                               | <b>2</b> 5 |

| 4 Operating modes                                                                             | <b>2</b> 6 |

| 4.1 Active mode                                                                               | <b>2</b> 6 |

| 4.2 Radio-on mode                                                                             | <b>2</b> 6 |

| 4.3 Deep Sleep modes                                                                          | <b>2</b> 6 |

| 4.3.1 Deep Sleep: 16 KB Data RAM and 64 KB RAM Retention mode                                 | 26         |

| 4.3.2 Deep Sleep: 16 KB Data RAM Retention mode                                               | 27         |

| 4.3.3 Deep Sleep: No RAM Retention and External Interrupts and Timer Enabled (Hibernate) mode | 27         |

| 4.3.4 Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode             | 27         |

| 5 Microcontroller, memory, and baseband logic                                                 | 28         |

| 5.1 Microcontroller                                                                           | 28         |

| 5.2 Memory                                                                                    | 28         |

| 5.2.1 RAM code and data (Internal)                                                            | 29         |

| 5.2.2 ROM (Internal)                                                                          | 29         |

| 5.2.3 OTP (Internal)                                                                          | 29         |

| 5.2.4 Flash (Internal)                                                                        | 30         |

| 6 Peripheral interfaces                                                                       | 31         |

| 6.1 I <sup>2</sup> C Master/Slave (General)                                                   | 32         |

| 6.2 SPI Master/Slave (General)                                                                | 32         |

| 6.3 SPI debug interface (QTIL proprietary)                                                    | 33         |

| 6.3.1 Instruction cycle                                                                       | 33         |

| 6.3.2 Multislave operation                                                                    | 33         |

| 6.4 UART (General)                                                                            | 33         |

| 6.4.1 UART configuration settings                                                             |            |

| 6.4.2 UART configuration while in Deep Sleep                                                  |            |

| 6.5 PWMs                                                                                      |            |

| 6.5.1 LED control PWM                                                                         |            |

| 6.6 Key scanner                                                                               |            |

| 6.7 Quadrature decoders                                                                       |            |

| 6.8 10-bit auxiliary ADC                                                                      | 36         |

| 7 Auxiliary features                                                                          | 37         |

| 7.1 Battery monitor                                                                           | 37         |

| 7.2 Temperature sensor                                                                        | 37         |

| 8 Programmable I/O ports, PIO, and AIO                                                        | 38         |

| 8.1 General PIOs                                                                              | 38         |

| 8.2 AIOs                                                                                      | 38         |

| 8.2.1 10-bit auxiliary ADC                                                                    | 38         |

| 8.3 Digital pin states on initial power-up                             |      |

|------------------------------------------------------------------------|------|

| 9 CSRB31024 LGA software stack                                         |      |

| 10 Power control and regulation                                        | . 42 |

| 10.1 Switch-mode regulator                                             | . 42 |

| 10.2 Reset                                                             | 42   |

| 11 CSRB31024 LGA example application schematic                         | 43   |

| 12 Electrical characteristics                                          | . 44 |

| 12.1 Absolute maximum ratings                                          | 44   |

| 12.2 Recommended operating conditions                                  | . 44 |

| 12.3 Input/output terminal characteristics                             | 45   |

| 12.3.1 Switch-mode regulator                                           | . 45 |

| 12.3.2 RF linear regulator                                             | . 46 |

| 12.3.3 Digital I/O terminals                                           | 46   |

| 12.3.4 AIO                                                             | . 46 |

| 13 Current consumption                                                 | . 47 |

| 14 Product reliability tests                                           | . 48 |

| 14.1 Automotive die test                                               | . 48 |

| 14.2 Automotive package test                                           | . 48 |

| 14.3 Life testing production limitations                               | 48   |

| 14.3.1 Early life fail rate                                            | 49   |

| 14.3.2 High temperature life testing                                   | . 49 |

| 14.3.3 HTOL: Mission profile analysis (Grade 3)                        | . 50 |

| 15 Environmental declaration statement for QTIL semiconductor products | . 51 |

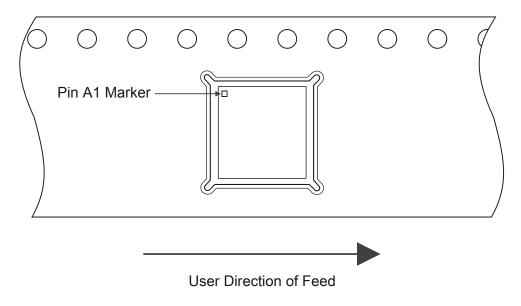

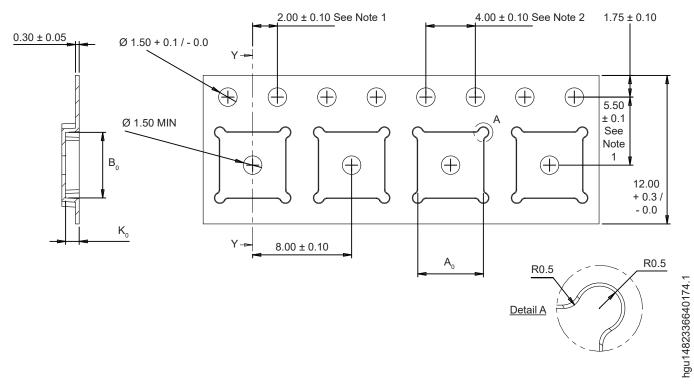

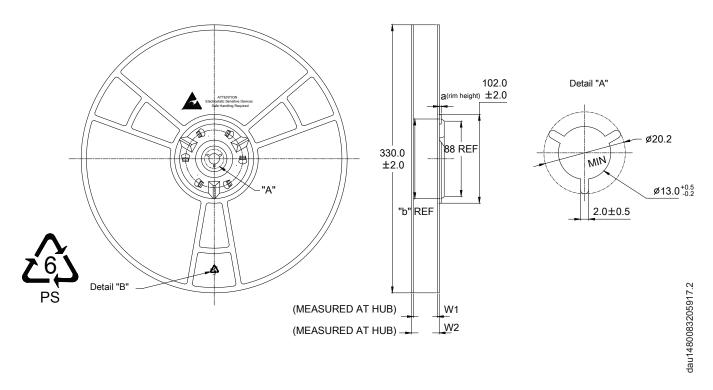

| 16 Tape and reel information                                           | . 52 |

| 16.1 Tape orientation                                                  | . 52 |

| 16.2 Tape dimensions                                                   | 53   |

| 16.3 Reel information                                                  | 54   |

| 16.4 Moisture sensitivity level                                        | . 54 |

| 17 Document references                                                 | 55   |

| 18 Terms and definitions                                               | 56   |

# **Tables**

| Table 1-1: CSRB31024 LGA chip marking content                                           | 14 |

|-----------------------------------------------------------------------------------------|----|

| Table 1-2: CSRB31024 LGA device terminal functions (Radio)                              | 16 |

| Table 1-3: CSRB31024 LGA device terminal functions (Synthesizer and oscillator)         | 16 |

| Table 1-4: CSRB31024 LGA device terminal functions (PIO port)                           | 16 |

| Table 1-5: CSRB31024 LGA device terminal functions (Test and debug)                     | 17 |

| Table 1-6: CSRB31024 LGA device terminal functions (Power supplies and control)         | 17 |

| Table 1-7: CSRB31024 LGA package dimensions table                                       | 20 |

| Table 3-1: Crystal specification                                                        | 24 |

| Table 6-1: Instruction cycle for an SPI transaction                                     | 33 |

| Table 6-2: UART signals                                                                 | 34 |

| Table 6-3: UART configuration settings                                                  | 34 |

| Table 8-1: CSRB31024 LGA 10-bit auxiliary ADC                                           | 38 |

| Table 8-2: Pin states on initial power-up                                               | 39 |

| Table 8-3: CSRB31024 LGA PIO configuration options                                      | 40 |

| Table 12-1: CSRB31024 LGA absolute maximum ratings                                      | 44 |

| Table 12-2: CSRB31024 LGA recommended operating conditions                              | 44 |

| Table 12-3: CSRB31024 LGA switch-mode regulator                                         | 45 |

| Table 12-4: CSRB31024 LGA RF linear regulator                                           | 46 |

| Table 12-5: CSRB31024 LGA input voltage levels                                          | 46 |

| Table 12-6: CSRB31024 LGA output voltage levels                                         | 46 |

| Table 12-7: CSRB31024 LGA input and tri-state                                           | 46 |

| Table 12-8: CSRB31024 LGA AIO                                                           | 46 |

| Table 13-1: Current consumption                                                         | 47 |

| Table 14-1: Automotive die test                                                         | 48 |

| Table 14-2: Automotive package test                                                     | 48 |

| Table 14-3: Test application activity voltage profile for early life fail rate          | 49 |

| Table 14-4: Test application activity voltage profile for high temperature life testing | 49 |

| Table 14-5: Example life-time temperature profile                                       | 50 |

| Table 15-1: Restricted substances present in QTIL products                              | 51 |

|                                                                                         |    |

| Table 16-1: CSRB31024 LGA tape dimensions | 53 |

|-------------------------------------------|----|

| Table 16-2: CSRB31024 LGA reel dimensions | 54 |

# **Figures**

| CSRB31024 LGA functional block diagram                   | 4  |

|----------------------------------------------------------|----|

| Figure 1-1: CSRB31024 LGA chip marking.                  | 14 |

| Figure 1-2: CSRB31024 LGA pinout diagram                 |    |

| Figure 1-3: CSRB31024 LGA package dimensions diagram     |    |

| Figure 3-1: CSRB31024 LGA clock architecture.            | 23 |

| Figure 3-2: Crystal driver circuit                       | 24 |

| Figure 5-1: Baseband digits block diagram                | 28 |

| Figure 6-1: Peripheral interfaces block diagram          | 31 |

| Figure 6-2: SPI timing diagram                           | 32 |

| Figure 6-3: Example keyboard matrix 3 x 2 size           | 35 |

| Figure 6-4: 10-bit auxiliary ADC reference               | 36 |

| Figure 9-1: Software architecture                        | 41 |

| Figure 11-1: CSRB31024 LGA example application schematic | 43 |

| Figure 16-1: CSRB31024 LGA tape orientation              |    |

| Figure 16-2: CSRB31024 LGA tape dimensions               | 53 |

| Figure 16-3: CSRB31024 LGA reel dimensions               | 54 |

# 1 Package information

CSRB31024 LGA is available in a 5 x 5 x 0.75 mm 36-lead LGA package.

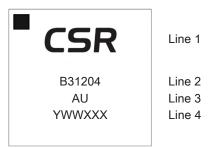

## 1.1 Chip marking

Chip marking identifies lot-specific information about CSRB31024 LGA.

Figure 1-1 shows the product marking for CSR-B31024-0-36BLGA-MT-00-0 in a 36-lead 5 x 5 x 0.75 mm LGA package.

Figure 1-1 CSRB31024 LGA chip marking

**NOTE** Figure 1-1 is not to scale. The marking font and image are for illustration purposes only.

The square location mark identifies pin 1.

Table 1-1 CSRB31024 LGA chip marking content

| Line | Description              | Definition                                                                               |

|------|--------------------------|------------------------------------------------------------------------------------------|

| 1    | CSR logo                 | -                                                                                        |

| 2    | Device number            | B31024                                                                                   |

| 3    | Device number            | AU                                                                                       |

| 4    | Manufacturing trace code | YWWXXX                                                                                   |

|      |                          | <ul><li>Y: Assembly year</li><li>WW: Assembly week</li><li>XXX: Lot designator</li></ul> |

# G-TW-0013000.1.3

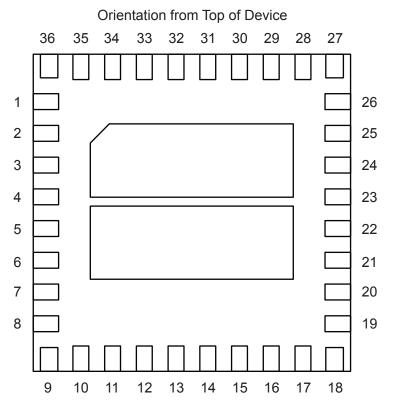

# 1.2 CSRB31024 LGA pinout diagram

The CSRB31024 LGA IC has 36 leads, numbered sequentially in an anticlockwise (counterclockwise) direction, starting from lead 1.

Figure 1-2 CSRB31024 LGA pinout diagram

## 1.3 Device terminal functions

The leads on the CSRB31024 LGA are grouped into various terminal functions. The device terminal functions include:

- Radio

- Synthesizer and oscillator

- PIO port

- Test and debug

- Power supplies and control

#### 1.3.1 Device terminal functions (Radio)

Table 1-2 CSRB31024 LGA device terminal functions (Radio)

| Radio | Lead | Pad type | Supply domain | Description                                        |

|-------|------|----------|---------------|----------------------------------------------------|

| RF    | 3    | RF       | VDD_RF        | Antenna port for Bluetooth transmitter / receiver. |

## 1.3.2 Device terminal functions (Synthesizer and oscillator)

Table 1-3 CSRB31024 LGA device terminal functions (Synthesizer and oscillator)

| Synthesizer and oscillator | Lead | Pad type | Supply domain | Description              |

|----------------------------|------|----------|---------------|--------------------------|

| XTAL_IN                    | 6    | Analog   | VDD_RF        | Reference clock input.   |

| XTAL_OUT                   | 5    | Analog   | VDD_RF        | Drive for clock crystal. |

# 1.3.3 Device terminal functions (PIO port)

Table 1-4 CSRB31024 LGA device terminal functions (PIO port)

| PIO port | Lead | Pad type                                                                       | Supply domain | Description                       |

|----------|------|--------------------------------------------------------------------------------|---------------|-----------------------------------|

| PIO[14]  | 20   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 14. |

| PIO[13]  | 1    | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 13. |

| PIO[12]  | 36   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 12. |

| PIO[11]  | 35   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 11. |

| PIO[10]  | 34   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 10. |

| PIO[9]   | 33   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 9.  |

Table 1-4 CSRB31024 LGA device terminal functions (PIO port) (cont.)

| PIO port | Lead | Pad type                                                                       | Supply domain | Description                      |

|----------|------|--------------------------------------------------------------------------------|---------------|----------------------------------|

| PIO[8]   | 32   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 8. |

| PIO[7]   | 30   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 7. |

| PIO[6]   | 29   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 6. |

| PIO[5]   | 28   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 5. |

| PIO[4]   | 27   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 4. |

| PIO[3]   | 25   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 3. |

| PIO[2]   | 24   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 2. |

| PIO[1]   | 23   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 1. |

| PIO[0]   | 22   | Digital: Bidirectional with programmable strength internal pull-up / pull-down | VDD_PADS      | General programmable I/O line 0. |

| AIO[0]   | 9    | Unidirectional analog                                                          | VDD_AUX       | Analog programmable input line.  |

## 1.3.4 Device terminal functions (Test and debug)

Table 1-5 CSRB31024 LGA device terminal functions (Test and debug)

| Test and debug | Lead | Pad type                             | Supply domain | Description                                                           |

|----------------|------|--------------------------------------|---------------|-----------------------------------------------------------------------|

| SPI_PIO#       | 21   | Input with strong internal pull-down | VDD_PADS      | Logic high switches PIO[3:0] to Debug SPI operation, low to PIO mode. |

# 1.3.5 Device terminal functions (Power supplies and control)

Table 1-6 CSRB31024 LGA device terminal functions (Power supplies and control)

| Power Supplies and Control | Lead | Description                                                       |

|----------------------------|------|-------------------------------------------------------------------|

| VDD_BAT                    | 10   | Positive supply from the battery.                                 |

| SMPS_LX1                   | 11   | Terminal 1 of the external 2.2 µH inductor connected to this pin. |

| SMPS_LX2                   | 12   | Terminal 2 of the external 2.2 µH inductor connected to this pin. |

| VDD_AUX                    | 15   | SMPS output for the auxiliary rail and AIO port.                  |

| VDD_DIG                    | 16   | SMPS output for the digital rail.                                 |

| VDD_MEM                    | 17   | SMPS output for the memory rail.                                  |

| VDD_RAD                    | 13   | SMPS output for the radio rail.                                   |

| VDD_RF_IN                  | 14   | SMPS output for the radio rail.                                   |

#### Table 1-6 CSRB31024 LGA device terminal functions (Power supplies and control) (cont.)

| Power Supplies and Control | Lead                           | Description                                                   |

|----------------------------|--------------------------------|---------------------------------------------------------------|

| VDD_RF                     | 7                              | Decoupled supply for radio and XTAL pads.                     |

| VSS_RF                     | 4, 2                           | Ground connection for RF.                                     |

| VDD_PADS                   | 26, 19                         | Positive supply for digital I/O ports PIO[14:0] and SPI_PIO#. |

| VSS                        | 31, 18, 8 and the central pads | Ground connections.                                           |

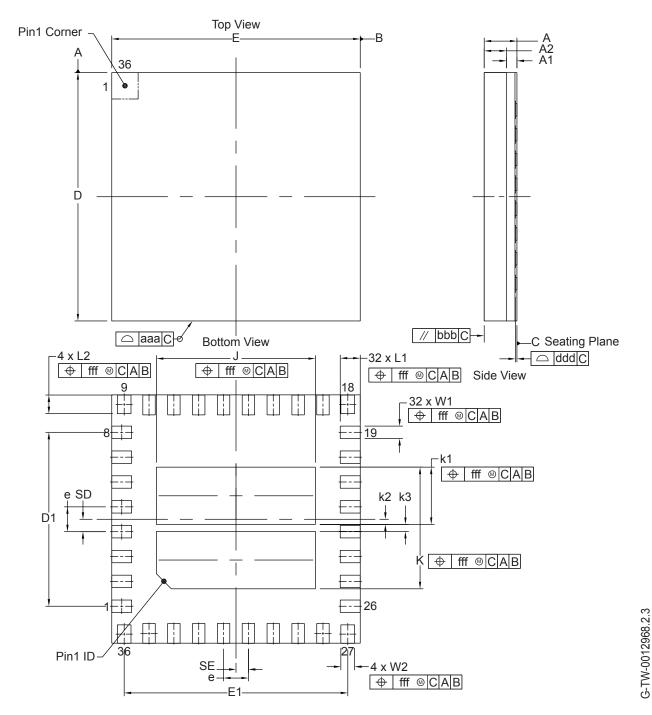

# 1.4 Package dimensions

CSRB31024 LGA is available in a 5 x 5 x 0.75 mm 36-lead LGA package.

#### Package dimensions diagram

Figure 1-3 CSRB31024 LGA package dimensions diagram

#### Package dimensions table

Table 1-7 CSRB31024 LGA package dimensions table

| Dimension   | Min                                                                                                                                                                                                                                                                                                                                                                                         | Тур                             | Max   | Dimension     | Min   | Тур   | Max   |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|---------------|-------|-------|-------|--|

| Α           | -                                                                                                                                                                                                                                                                                                                                                                                           | 0.66                            | 0.75  | k2            | -     | 0.105 | -     |  |

| A1          | -                                                                                                                                                                                                                                                                                                                                                                                           | 0.21                            | -     | k3            | -     | 0.140 | -     |  |

| A2          | -                                                                                                                                                                                                                                                                                                                                                                                           | 0.45                            | -     | L1            | 0.35  | 0.4   | 0.45  |  |

| D and E     | 4.9                                                                                                                                                                                                                                                                                                                                                                                         | 5.0                             | 5.1   | L2            | 0.325 | 0.375 | 0.425 |  |

| D1          | -                                                                                                                                                                                                                                                                                                                                                                                           | 3.5                             | -     | SD and SE     | -     | 0.25  | -     |  |

| E1          | -                                                                                                                                                                                                                                                                                                                                                                                           | 4.5                             | -     | W1            | 0.2   | 0.25  | 0.3   |  |

| е           | -                                                                                                                                                                                                                                                                                                                                                                                           | 0.5                             | -     | W2            | 0.225 | 0.275 | 0.325 |  |

| J           | 3.15                                                                                                                                                                                                                                                                                                                                                                                        | 3.20                            | 3.25  | aaa, bbb, fff | -     | 0.1   | -     |  |

| K           | 2.40                                                                                                                                                                                                                                                                                                                                                                                        | 2.45                            | 2.50  | ddd           | -     | 0.08  | -     |  |

| k1          | 1.105                                                                                                                                                                                                                                                                                                                                                                                       | 1.155                           | 1.205 | -             | -     | -     | -     |  |

| Notes       | <ol> <li>Dimensioning and tolerances conform to ASME Y14.5M 1994.</li> <li>Pin #1 identifier is placed on the top surface of the package. Exact shape and size of this feature is optional.</li> <li>Parallelism measurement excludes any effect of marks on the top surface of the package.</li> <li>The 4 leads (9, 18, 27 and 36) are wider and shorter than all other leads.</li> </ol> |                                 |       |               |       |       |       |  |

| Description | 36-lead Land                                                                                                                                                                                                                                                                                                                                                                                | 36-lead Land Grid Array Package |       |               |       |       |       |  |

| Size        | 5 x 5 x 0.75 mm                                                                                                                                                                                                                                                                                                                                                                             |                                 |       |               |       |       |       |  |

| Pitch       | 0.5                                                                                                                                                                                                                                                                                                                                                                                         |                                 |       | Units         | ts mm |       |       |  |

# 1.5 PCB design and assembly considerations

This section lists recommendations to achieve maximum board-level reliability of the 5 x 5 x 0.75 mm LGA 36-lead package:

- NSMD lands (lands smaller than the solder mask aperture) are preferred, because of the greater accuracy of the metal definition process compared to the solder mask process. With solder mask defined pads, the overlap of the solder mask on the land creates a step in the solder at the land interface, which can cause stress concentration and act as a point for crack initiation.

- QTIL recommends that the PCB land pattern is in accordance with IPC standard IPC-7351.

- Solder paste must be used during the assembly process.

# 1.6 Typical solder reflow profile

For information, see Typical Solder Reflow Profile for Lead-free Devices Information Note (80-CT462-1).

# 2 Bluetooth modem

CSRB31024 LGA's modern supports Bluetooth low energy technology and has four link controller blocks supporting up to four connections.

## 2.1 RF port

CSRB31024 LGA contains a single-ended 50  $\Omega$  RF Tx / Rx port pin. No external matching to 50  $\Omega$  is required.

NOTE The antenna must be connected when CSRB31024 LGA is powered up. Significant changes in VSWR after the chip has performed start of day calibrations might result in Tx modulation errors and reduced Rx sensitivity.

#### 2.2 RF receiver

The receiver features a near-zero IF architecture enabling the channel filters to be integrated onto the die. Sufficient out-of-band blocking provided on die at the LNA input enables the receiver to be used close to cellular phone transmitters without being significantly desensitized:

- Receive sensitivity is typically-90.0 dBm

- Software selectable Boost mode can be enabled for extra sensitivity

- An AGC supports the device to meet Bluetooth v5.0 specification

- Receiver large input level saturation is typically -5 dBm

NOTE CSRB31024 LGA does not support control for an external LNA. The additional front-end gain from an LNA would compromise the Bluetooth maximum input signal level test RCV-LE/CA/BV-06-C.

#### 2.2.1 RSSI

Front-end LNA gain is changed according to measured RSSI, keeping the first mixer input signal within a limited range. This improves the dynamic range of the receiver, improving performance in interference-limited environments. The level is reported to the firmware using an API with accuracy of ±6 dBm, and resolution of 1 dBm.

**NOTE** This value is only available to an application after reception of a valid packet.

#### 2.3 RF transmitter

#### 2.3.1 Power amplifier

The internal PA can deliver a maximum of 4 dBm at the RF pin into a 50  $\Omega$  load. Configurable software enables delivery of lower output powers to reduce current consumption during transmit.

# 2.4 Bluetooth radio synthesizer

The Bluetooth radio synthesizer is fully integrated onto the die with no requirement for external components and meets all lock-time requirements of the Bluetooth v5.0 specification.

## 2.5 Baseband

# 2.5.1 Physical layer hardware engine

Dedicated logic performs:

- Cyclic redundancy check

- Encryption

- Data whitening

- Access code correlation

# 3 Clock generation

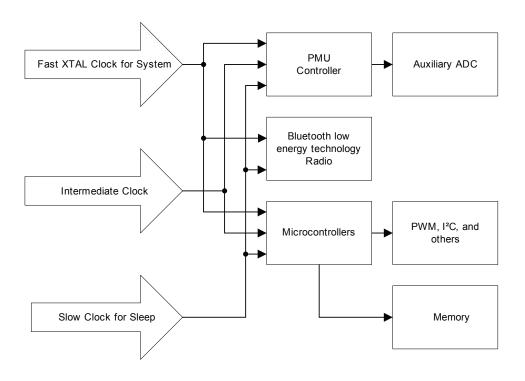

#### 3.1 Clock architecture

Figure 3-1 shows CSRB31024 LGA's three clocks:

- Fast Clock:

- Bluetooth system reference clock required for Tx and Rx

- Supplied by an external 32 MHz crystal

- Intermediate Clock:

- Internal clock source that can operate at various intermediate frequencies (62.5 kHz to 8 MHz in approximate log spacing)

- Suitable for peripherals that require a moderate clock frequency of low accuracy

- Lower power than Fast Clock and can work in Deep Sleep

- Slow Clock:

- Internal clock source

- Lowest power and works in Deep Sleep

- A digital state machine uses temperature sampling to ensure clock drift for sleep timing stays within 500 ppm

- Internally generated, running at approximately 32 kHz, without trim, only calibration

Figure 3-1 CSRB31024 LGA clock architecture

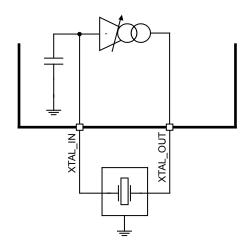

# 3.2 Crystal oscillator: XTAL\_IN and XTAL\_OUT

CSRB31024 LGA has a crystal driver circuit. This operates with an external crystal to form a Pierce oscillator. Figure 3-2 shows how the external crystal is connected to pins XTAL\_IN and XTAL\_OUT.

**NOTE** The crystal oscillator requires no external capacitors.

Figure 3-2 Crystal driver circuit

**NOTE** The PCB design must ensure that the total trace capacitance on XTAL\_IN and XTAL\_OUT are less than 2 pF each.

# 3.2.1 Crystal specification

Table 3-1 lists the specification required for a CSRB31024 LGA external crystal.

NOTE Crystals with the specification in Table 3-1 are produced by a limited number of manufacturers. QTIL recommends only using crystals listed in CSR102x Recommended Crystals Specification.

Table 3-1 Crystal specification

| Parameter                  | Description                                             | Min | Тур | Max | Unit   |

|----------------------------|---------------------------------------------------------|-----|-----|-----|--------|

| F <sub>nom</sub>           | Nominal fundamental frequency                           | -   | 32  | -   | MHz    |

| T <sub>stg</sub>           | Storage temperature                                     | -40 | -   | 125 | °C     |

| T <sub>op_automotive</sub> | Operating Temperature range                             | -40 | -   | 85  | °C     |

| C <sub>P</sub>             | Package capacitance (32 MHz)                            | -   | 0.8 | -   | pF     |

| C <sub>L</sub>             | Load capacitance                                        | -   | 6   | -   | pF     |

| F_tol_nom                  | Frequency Tolerance nominal at room temperature         | -10 | -   | 10  | ppm    |

| F_tol_temp_auto a          | Frequency stability over temperature (automotive)       | -20 | -   | 20  | ppm    |

| F_tol_aging                | Frequency tolerance aging 1st year @ 25°C               | -3  | -   | 3   | ppm/yr |

| Sensitivity                | Frequency variation vs. load capacitance changes @ 25°C | -   | 30  | 40  | ppm/pF |

| ESR                        | Motional Resistance (32 MHz)                            | -   | 20  | 60  | Ω      |

<sup>&</sup>lt;sup>a</sup> Wider temperature range (than industrial) requires a wider ppm tolerance

## 3.2.2 Crystal configuration

The crystal must be configured on each device during the manufacturing process.

NOTE For information about crystal configuration, see CSR102x Initial Configuration for Devices (80-CF263-1) (part of Qualcomm Bluetooth Low Energy SDK).

# 3.3 Sleep clock

CSRB31024 LGA uses the internal slow clock or crystal in low-power mode, eliminating the need for an externally supplied sleep clock.

# 4 Operating modes

CSRB31024 LGA has six operating modes. Four are Deep Sleep modes:

- Active mode

- Radio-on mode

- Deep Sleep modes:

- Deep Sleep: 16 KB Data RAM and 64 KB RAM Retention mode

- Deep Sleep: 16 KB Data RAM Retention mode

- Deep Sleep: No RAM Retention and External Interrupts and Timer Enabled (Hibernate) mode

- Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode

#### 4.1 Active mode

In Active mode, the processor runs:

- Code and/or performs activities with peripherals.

- With at least one link controller powered.

#### 4.2 Radio-on mode

In Radio-on mode, the Bluetooth radio is turned on.

**NOTE** Radio-on mode can only be entered from Active mode.

# 4.3 Deep Sleep modes

CSRB31024 LGA has four Deep Sleep modes.

#### 4.3.1 Deep Sleep: 16 KB Data RAM and 64 KB RAM Retention mode

In Deep Sleep: 16 KB Data RAM and 64 KB RAM Retention mode:

- Normal operation uses only the slow clock or intermediate clock (running at a slow speed).

- CSRB31024 LGA supports activity in peripherals to perform a particular operation (for example PWMs, keyboard scanner) or wake the chip on activity (for example UART, application SPI).

- Link controller state is maintained: This can be active (advertising, scanning or in a connection) and CSRB31024 LGA can deep sleep between periods on or around radio activity.

- A PIO deep sleep timer time-out or optional temperature change or low battery can wake the chip by generating an interrupt.

- It is possible to keep the processor powered and its power-controlled using power gating.

#### 4.3.2 Deep Sleep: 16 KB Data RAM Retention mode

In Deep Sleep: 16 KB Data RAM Retention mode:

- Normal operation uses only the slow clock or intermediate clock (running at a slow speed).

- CSRB31024 LGA supports activity in peripherals to perform a particular operation (for example PWMs, keyboard scanner) or wake the chip on activity (for example UART, application SPI).

- Link controller state is maintained: This can be active (advertising, scanning or in a connection) and CSRB31024 LGA can deep sleep between periods on or around radio activity.

- A PIO deep sleep timer time-out or optional temperature change or low battery can wake the chip by generating an interrupt.

- It is possible to keep the processor powered and its power-controlled using power gating.

# 4.3.3 Deep Sleep: No RAM Retention and External Interrupts and Timer Enabled (Hibernate) mode

In Deep Sleep: No RAM Retention and External Interrupts and Timer Enabled (Hibernate) mode:

- VDD BAT must always be present.

- A PIO can wake the chip (programmable as in Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode).

- The following can wake the chip:

- PIO hibernate timer time-out.

- Temperature change.

- Low battery.

## 4.3.4 Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode

In Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode:

- An attached battery can be used as a wake-up.

- No timers run, therefore CSRB31024 LGA can only be woken by a PIO or a rise on VDD\_BAT.

- VDD BAT can be removed if VDD PADS remains powered, because the pull states of pads are preserved.

- Ignore a rise on VDD\_BAT until a PIO has latched an event (enabling two different Deep Sleep: No RAM Retention and External Interrupts Enabled submodes).

- The PIOs that CSRB31024 LGA is sensitive to on wake-up are programmable; that is, it is possible to ignore events on some PIOs but not others.

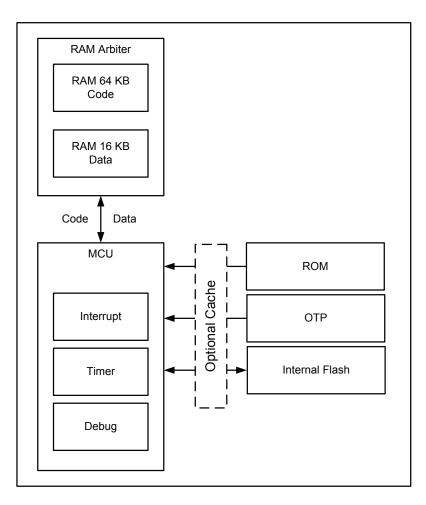

Figure 5-1 Baseband digits block diagram

## 5.1 Microcontroller

The MCU, interrupt controller, and event timer run the Bluetooth software stack and control the Bluetooth radio and external interfaces. A 16-bit RISC microcontroller is used for low power consumption and efficient use of memory.

# 5.2 Memory

CSRB31024 LGA memory includes:

- RAM code and data (Internal)

- ROM (Internal)

- OTP (Internal)

- Flash (Internal)

Memory spaces include:

- Application Store: A storage area for customer applications, located in OTP or SPI flash.

- Configuration Store: An area of memory used to store configuration settings (ROM, OTP, RAM, SPI flash).

- User Store: OTP (programmable once then read-only) and SPI flash data storage available to user applications at runtime.

#### 5.2.1 RAM code and data (Internal)

CSRB31024 LGA has RAM for code and data.

**NOTE** Either RAM is available for code or data.

#### Code RAM

- 64 KB: For code or data

- Primary use for developing applications for eventual storage in OTP memory

- Useable as a cache for applications stored in flash or OTP memory

- Useable as code or data RAM if not used as a code cache

- Software provides details of the area of shared RAM to the user application

- Part or all of the code RAM is powered down to save power when not in use

#### **Data RAM**

- 16 KB: For code or data

- Primary use for firmware and applications

- The use of all data RAM for executing code is possible (although there are some restrictions on when this can be done)

## 5.2.2 ROM (Internal)

System firmware is implemented in 192 KB of internal ROM.

NOTE Code executes from ROM and RAM.

# 5.2.3 OTP (Internal)

60 KB of OTP is available for storage of user applications:

- One-time programmable

- Enables reading and writing of information to the configuration store

- Enables downloading of software

- Has a storage provider driver

- PMU supplies power

- Useable space to store a boot loader or fall-back image for deploying updateable applications in Flash

#### 5.2.4 Flash (Internal)

256 KB of flash (internal) memory is available for user applications:

- More than 100,000 erase/write cycles<sup>1</sup>.

- Internal flash is accessed at a speed lower than the processor can run: This means that application code executing from flash executes slower than that in OTP (or RAM). To mitigate this use code RAM as a cache.

**NOTE** For information about flash configuration, see *CSR102x Initial Configuration for Devices* (80-CF263-1) (part of Qualcomm Bluetooth Low Energy SDK).

- Encrypted applications have a maximum size of 64 KB. This is because the image is copied to the code RAM and decrypted in place using the decryption key stored in OTP. For more information, see the SDK software release note.

- Up to 20 years data retention<sup>1</sup>.

Erase/write cycle and data retention are trade-off parameters, and dependent on application mission profiles, for example temperature.

Figure 6-1 Peripheral interfaces block diagram

# 6.1 I<sup>2</sup>C Master/Slave (General)

CSRB31024 LGA has 1 I<sup>2</sup>C master/slave general interface for communication with external peripherals and sensors:

- Maximum clock speed 1 MHz

- Data transmiting/receiving of variable byte length

- 7-bit and 10-bit addressing modes

- Configurable:

- PIO pins for SCL and SDA

- I<sup>2</sup>C clock: 100 kHz default (software-configurable) at 1:1 duty-cycle (asymmetric if necessary)

- Supports slave clock stretching

- CSRB31024 LGA is Fast Mode and Fast Mode+ compatible.

**NOTE** Strong pull-up is typically sufficient for I<sup>2</sup>C on all PIO pads.

# 6.2 SPI Master/Slave (General)

CSRB31024 LGA has one SPI master/slave general interface for communication with other devices. CSRB31024 LGA supports:

- SPI master and slave

- All four modes supported

- Two methods of transferring data to memory:

- DMA to/from memory:

- 8-bit or 16-bit word size

- Big and little-endian

- Software reads and writes to FIFOs: variable from 1-bit to 16-bits

- Interrupt callbacks to processor enable SPI as a slave to indicate that it requires service

- Deep sleep mode (depending on clock)

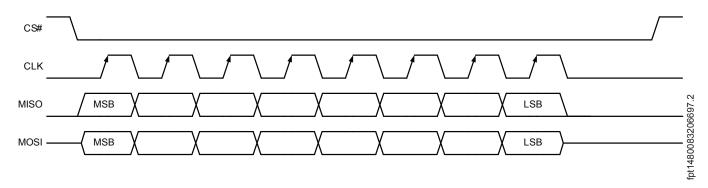

Figure 6-2 shows a simple SPI timing diagram.

Figure 6-2 SPI timing diagram

# 6.3 SPI debug interface (QTIL proprietary)

#### **NOTE**

The CSRB31024 LGA debug SPI interface is available in SPI slave mode to enable an external MCU to program and control the CSRB31024 LGA, via libraries or tools supplied by QTIL. The protocol of this interface is proprietary. A 128-bit lock key is applicable to secure the application code. The four SPI debug lines directly support this function on PIO[3:0].

Debug SPI access is required for programming, configuring and debugging the CSRB31024 LGA. It is required in production. Ensure the four SPI signals and SPI\_PIO# are brought out to either test points or a header with SPI\_PIO#.

To enable the SPI debug feature on PIO[3:0], take SPI\_PIO# high.

CSRB31024 LGA uses a 16-bit data and 16-bit address programming and debug interface. Transactions occur when the internal processor is running or is stopped.

Data is written or read one word at a time, or the auto-increment feature is available for block access.

#### 6.3.1 Instruction cycle

The CSRB31024 LGA is the slave and receives commands on SPI\_MOSI and outputs data on SPI\_MISO. Table 6-1 lists the instruction cycle for an SPI transaction.

Table 6-1 Instruction cycle for an SPI transaction

| Number | Transaction Instruction  |                                                 |

|--------|--------------------------|-------------------------------------------------|

| 1      | Reset the SPI interface  | Hold SPI_CS# high for 2 SPI_CLK cycles          |

| 2      | Write the command word   | Take SPI_CS# low and clock in the 8-bit command |

| 3      | Write the address        | Clock in the 16-bit address word                |

| 4      | Write or read data words | Clock in or out 16-bit data word/s              |

| 5      | Termination              | Take SPI_CS# high                               |

Except for reset, hold SPI\_CS# low during the transaction. Data on SPI\_MOSI is clocked into the CSRB31024 LGA rising edge of the clock line SPI\_CLK. When reading, CSRB31024 LGA replies to the master on SPI\_MISO with the data changing on the falling edge of the SPI\_CLK. The master provides the clock on SPI\_CLK. The transaction is terminated by taking SPI\_CS# high.

The auto increment operation on the CSRB31024 LGA cuts down on the overhead of sending a command word and the address of a register for each read or write. This is especially true when large amounts of data are to be transferred. The auto increment offers increased data transfer efficiency on the CSRB31024 LGA. To invoke auto increment, SPI\_CS# is kept low, which auto increments the address while providing an extra 16 clock cycles for each extra word written or read.

#### 6.3.2 Multislave operation

Do not connect the CSRB31024 LGA in a multislave arrangement by simple parallel connection of slave MISO lines. When CSRB31024 LGA is deselected (SPI\_CS# = 1), the SPI\_MISO line does not float. Instead, CSRB31024 LGA may output 0 if the processor is running or 1 if it is stopped.

# 6.4 UART (General)

The CSRB31024 LGA UART interface provides a simple mechanism to communicate with other serial devices using the RS232 protocol.

Table 6-2 lists the four signals that implement the UART function in CSRB31024 LGA. Hardware flow control using RTS/CTS lines is optional.

Table 6-2 UART signals

| Signal   | Description                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------|

| UART_RX  | Pin to receive UART data from another device                                                          |

| UART_TX  | Pin to transmit UART data to another device                                                           |

| UART_CTS | Pin for another device to indicate it is ready to receive data (active low input)                     |

| UART_RTS | Pin for another device to indicate that this other device is ready to receive data (active low input) |

#### 6.4.1 UART configuration settings

$UART\ configuration\ parameters,\ for\ example\ baud\ rate\ and\ data\ format,\ are\ set\ using\ CSRB31024\ LGA\ firmware.$

Table 6-3 lists UART configuration settings for CSRB31024 LGA.

Table 6-3 UART configuration settings

| Parameter                                |            | Possible values      |            |  |

|------------------------------------------|------------|----------------------|------------|--|

| Baud rate <sup>a</sup> Internal RC clock |            | ≤ 7200               | <2 % Error |  |

|                                          |            | 7200 < baud ≤ 115200 | <5 % Error |  |

|                                          | XTAL clock | > 115200             | <1 % Error |  |

| Parity                                   |            | None, Odd or Even    |            |  |

| Number of stop bits                      |            | 1 or 2               |            |  |

| Bits per byte                            |            | 8                    |            |  |

<sup>&</sup>lt;sup>a</sup> For more information, see the SDK release note.

# 6.4.2 UART configuration while in Deep Sleep

The maximum baud rate is 2400 baud during deep sleep.

#### 6.5 PWMs

CSRB31024 LGA has five independently configurable PWM instances.

A multipurpose PWM generator provides two modes:

- Normal PWM mode:

- For motor control and general-purpose PWM

- LED mode:

- For LED fading

#### 6.5.1 LED control PWM

CSRB31024 LGA has four LED mode PWM blocks (2 x fast / 2 x slow). Each LED mode PWM has an 8-bit resolution for all configuration registers and a:

- Minimum brightness duty cycle (grouped in a 16-bit wide register)

- Maximum brightness duty cycle (grouped in a 6-bit wide register)

- Hold Minimum and Maximum time (grouped in a 16-bit wide register)

- Step (ramp) time

- Brightness configuration specified in units of typically 30 µs assuming a 32 kHz clock

- Hold times specified in units of typically 16 ms assuming a 32 kHz clock

- Step time specified in units of typically 1 ms assuming a 32 kHz clock

NOTE CSRB31024 LGA supports immediate reconfiguration on the sync register write.

## 6.6 Key scanner

CSRB31024 LGA has one key scanner for applications such as mouse and keyboard HID.

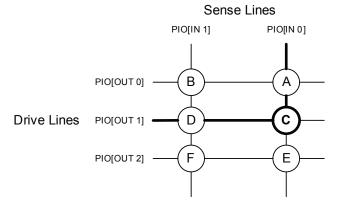

Figure 6-3 shows an example keyboard matrix at a size of 3 x 2 (PIO drive lines x PIO sense lines respectively).

Figure 6-3 Example keyboard matrix 3 x 2 size

Physical buttons are on line crossings A to F. If a button is pressed both lines become connected. Assuming sense lines are pulled-up by internal logic, a keypress, for example C is detectable by forcing PIO[OUT 1] low and reading 0 on PIO[IN 0].

It supports:

- Keypad matrix up to 12 PIO inputs (sense lines) and 18 PIO outputs (drive lines):

- Drives 1 to 18 drive lines consecutively

- 12-bit key registers updated every scan

- Press and release events reported to the host via callback

- Variable scan rate:

- By default drives consecutive drive lines every clock cycle

- Configurable number of clocks per drive line

**NOTE** The key scanner does not support ghost key removal.

The key scanner configuration and control includes:

- PIO pin numbers to be used for drive and sense lines

- Scan rate, Hz, and active/idle ratio

- Hardware starting and stopping

- Callback creation to receive keyboard map data.

## 6.7 Quadrature decoders

CSRB31024 LGA has four quadrature decoders with:

- Each having a configurable simple filter on inputs (for debouncing)

- Enabling and disabling of single or multiple decoders

- Data reading functionality

- Processor interrupt generation

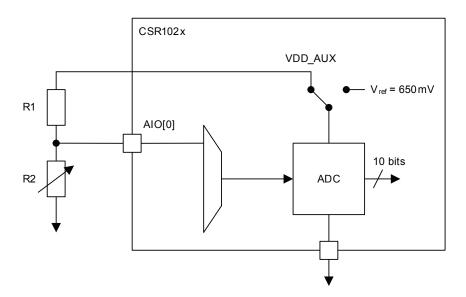

# 6.8 10-bit auxiliary ADC

CSRB31024 LGA has a single 10-bit auxiliary ADC:

- A resistive SAR ADC

- Attached to one AIO pad

- The processor has access to its ADC result value after exit from Deep Sleep mode

- The ADC reference is VDD\_AUX, see Figure 6-4.

Figure 6-4 10-bit auxiliary ADC reference

NOTE Figure 6-4 shows an extra internal 650 mV reference. This is for QTIL test purposes only.

The 10-bit Auxiliary ADC is not available during XTAL start up or battery voltage and temperature monitoring. Therefore, if the hardware is already using the ADC, the time to perform a conversion may be longer.

### 7 Auxiliary features

### 7.1 Battery monitor

CSRB31024 LGA contains an internal battery monitor that reports the battery voltage to the software.

### 7.2 Temperature sensor

CSRB31024 LGA contains a sensor that can report the chip temperature in °C using a firmware API.

### 8 Programmable I/O ports, PIO, and AIO

This section describes CSRB31024 LGA PIO and AIO.

#### 8.1 General PIOs

15 lines of programmable bidirectional I/O are provided:

- May be set by the application code or used as an input or to wake the chip.

- Software-configurable as weak pull-up, weak pull-down, strong pull-up, or strong pull-down.

- At reset all lines are inputs with weak pull-down.

- Pull strength, direction, and pad states preserved across all nonoff states to support waking on any PIO (even when VDD\_DIG is powered down).

- Configurable to wake CSRB31024 LGA via an individually selectable mask for rising, falling or any edge transition from Deep Sleep: No RAM Retention and External Interrupts Enabled, Deep Sleep: 16 KB Data RAM Retention or Deep Sleep: 16 KB Data RAM and 64 KB RAM Retention mode.

- Available as interrupt request lines.

- Powered from VDD\_PADS

NOTE VDD PADS must remain powered.

QTIL cannot guarantee that the PIO assignments remain as described. Implementation of the PIO lines is firmware build-specific, for more information see the relevant software release note.

#### 8.2 AIOs

CSRB31024 LGA has one pin providing a unidirectional analog programmable input line, AIO[0].

**NOTE** This pin does not provide an output capability.

#### 8.2.1 10-bit auxiliary ADC

Table 8-1 CSRB31024 LGA 10-bit auxiliary ADC

| 10-bit auxiliary ADC             | Min  | Тур  | Max     | Unit      |

|----------------------------------|------|------|---------|-----------|

| Resolution                       | -    | -    | 10      | Bits      |

| Input voltage range <sup>a</sup> | 0    | -    | VDD_AUX | V         |

| Input bandwidth                  | -    | 100  | -       | kHz       |

| Conversion time                  | 1.38 | 1.69 | 4.14    | μs        |

| Sample rate <sup>b</sup>         | -    | -    | 700     | Samples/s |

a LSB size = VDD AUX/1023.

b The 10-bit auxiliary ADC is accessed through the firmware API. The sample rate given is achieved as part of this function.

### 8.3 Digital pin states on initial power-up

Table 8-2 shows the pin states of CSRB31024 LGA on initial power-up. Pull-up and pull-down default to weak values unless specified otherwise.

Table 8-2 Pin states on initial power-up

| Pin name / Group | On initial power-up |

|------------------|---------------------|

| SPI_PIO#         | Strong Pull-Down    |

| All other PIOs   | Weak Pull-Down      |

### **PIO configuration options**

Table 8-3 lists CSRB31024 LGA PIO configuration options.

Table 8-3 CSRB31024 LGA PIO configuration options

|         |                 |     | SPI (G | eneral) |      |           | UART ( | General) |   | re decoder<br>out <sup>a</sup> |                      | Keys  | Scan  | TMR     | RCTR    |

|---------|-----------------|-----|--------|---------|------|-----------|--------|----------|---|--------------------------------|----------------------|-------|-------|---------|---------|

| PIO pin | l²C master only | ССК | CS#    | MISO    | MOSI | Debug SPI | Data   | Flow     | A | В                              | LED/PWM <sup>b</sup> | Drive | Sense | Timer 0 | Timer 1 |

| PIO[14] | SCL             | Y   | Y      | Y       | Y    | -         | TX     | RTS      | Y | Y                              | Υ                    | Υ     | Y     | Y       | Y       |

| PIO[13] | SDA             | Y   | Υ      | Υ       | Y    | -         | RX     | CTS      | Y | Y                              | Υ                    | Υ     | Y     | Υ       | Y       |

| PIO[12] | SCL             | Y   | Υ      | Y       | Y    | -         | TX     | RTS      | Y | Y                              | Υ                    | Υ     | Y     | Y       | Y       |

| PIO[11] | SDA             | Y   | Υ      | Y       | Y    | -         | RX     | CTS      | Y | Y                              | Υ                    | Y     | Y     | Y       | Y       |

| PIO[10] | SCL             | Y   | Υ      | Υ       | Y    | -         | TX     | RTS      | Υ | Y                              | Υ                    | Y     | Y     | Y       | Y       |

| PIO[9]  | SDA             | Y   | Y      | Υ       | Υ    | -         | RX     | CTS      | Y | Y                              | Υ                    | Y     | Υ     | Υ       | Y       |

| PIO[8]  | SCL             | Y   | Y      | Y       | Y    | -         | TX     | RTS      | Y | Y                              | Υ                    | Y     | Y     | Y       | Y       |

| PIO[7]  | SDA             | Y   | Υ      | Υ       | Y    | -         | RX     | CTS      | Υ | Y                              | Υ                    | Υ     | Y     | Y       | Y       |

| PIO[6]  | SCL             | Y   | Y      | Υ       | Y    | -         | TX     | RTS      | Y | Y                              | Υ                    | Y     | Y     | Y       | Y       |

| PIO[5]  | SDA             | Y   | Y      | Y       | Y    | -         | RX     | CTS      | Υ | Y                              | Υ                    | Y     | Y     | Y       | Y       |

| PIO[4]  | SCL             | Y   | Υ      | Y       | Y    | -         | TX     | RTS      | Υ | Y                              | Υ                    | Y     | Y     | Υ       | Y       |

| PIO[3]  | SDA             | Y   | Y      | Y       | Y    | MISO      | RX     | CTS      | Y | Y                              | Y                    | Y     | Y     | Y       | Y       |

| PIO[2]  | SCL             | Y   | Υ      | Υ       | Υ    | MOSI      | TX     | RTS      | Y | Y                              | Υ                    | Y     | Υ     | Υ       | Y       |

| PIO[1]  | SDA             | Y   | Y      | Y       | Y    | CS#       | RX     | CTS      | Υ | Y                              | Y                    | Y     | Y     | Υ       | Y       |

| PIO[0]  | SCL             | Y   | Y      | Y       | Y    | CLK       | TX     | RTS      | Y | Y                              | Υ                    | Y     | Y     | Y       | Y       |

Quadrature decoder input A and B both require 4 PIOs to be assigned.

LED/PWM require 5 PIOs to be assigned to access all functionality.

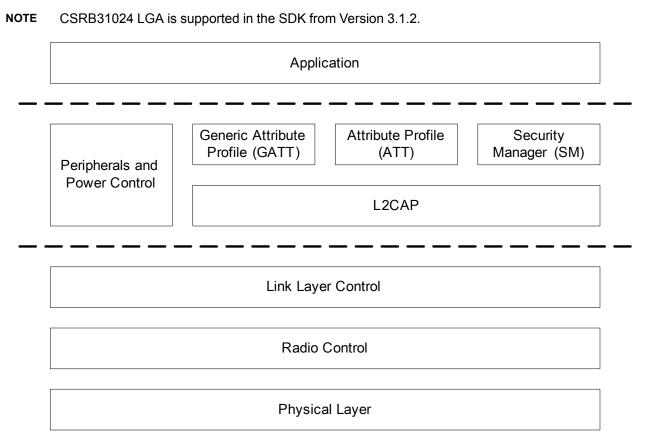

### **9** CSRB31024 LGA software stack

CSRB31024 LGA is supplied with Bluetooth v5.0 specification compliant stack firmware. Figure 9-1 shows that the CSRB31024 LGA software architecture enables the Bluetooth processing and the application program to run on the internal RISC MCU.

Figure 9-1 Software architecture

### **10** Power control and regulation

CSRB31024 LGA contains a switch-mode regulator that generates all the supply rails required from the battery.

### 10.1 Switch-mode regulator

The switch-mode regulator generates the four output voltage rails from the battery supply, VDD\_BAT.

The switch-mode regulator generates all required voltage rails for the system to operate using only a single inductor. No user intervention is required; the regulator automatically changes from buck to boost mode depending on the battery voltage and output voltage of the rails.

The voltage output is dynamically changed dependent on the mode of operation.

**NOTE** Each rail is only charged when, after sampling, it is below the comparator threshold.

### **10.2** Reset

CSRB31024 LGA processor is reset by:

- Power-on reset

- Software-configured watchdog timer

- Exit from Deep Sleep: No RAM Retention and External Interrupts and Timer Enabled (Hibernate) mode

- Exit from Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode

The PMU is reset by exit from Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode.

To fully reset the PIO pads take all of VDD\_PADS, VDD\_BAT, VDD\_AUX, VDD\_RAD and VDD\_MEM pins below 0.4 V.

If VDD\_BAT is removed from CSRB31024 LGA while not in Deep Sleep: No RAM Retention and External Interrupts Enabled (Dormant) mode, the PIO pads must be fully reset as described.

**NOTE** VDD\_BAT input voltage must drop to 0.4 V to guarantee a rising VDD\_BAT is seen by the PMU on reassertion.

VDD\_BAT typically takes approximately 20 s to drop to 0 V when power is removed due to circuit decoupling capacitance.

### 11 CSRB31024 LGA example application schematic

Figure 11-1 CSRB31024 LGA example application schematic

### 12 Electrical characteristics

### 12.1 Absolute maximum ratings

**NOTE** Exceeding absolute maximum ratings causes permanent damage to the CSRB31024 LGA. Exposure to any absolute maximum rating for extended periods of time affects reliability.

Table 12-1 CSRB31024 LGA absolute maximum ratings

| Rating                              | Min | Тур | Max  | Unit |

|-------------------------------------|-----|-----|------|------|

| Storage temperature                 | -40 | -   | 85   | °C   |

| Battery (VDD_BAT and VDD_PADS)      | 0   | -   | 3.6  | V    |

| I/O supply voltage                  | 0   | -   | 3.6  | V    |

| I/O supply (VDD_PADS) total current | -   | -   | 30   | mA   |

| VDD_AUX, VDD_DIG, AIOs              | 0   | -   | 1.26 | V    |

| VDD_RAD, VDD_RF_IN, VDD_RF          | 0   | -   | 2.2  | V    |

| XTAL_IN, XTAL_OUT                   | 0   | -   | 0.8  | V    |

| RF                                  | -   | -   | 0    | dBm  |

### 12.2 Recommended operating conditions

Use the CSRB31024 LGA recommended operating conditions to ensure optimum performance and reliability.

Table 12-2 CSRB31024 LGA recommended operating conditions

| Operating condition           | Min | Тур | Max | Unit |

|-------------------------------|-----|-----|-----|------|

| Operating temperature range   | -40 | 20  | 85  | °C   |

| Battery (VDD_BAT)             | 2.7 | 3.0 | 3.3 | V    |

| I/O supply voltage (VDD_PADS) | 2.7 | 3.0 | 3.3 | V    |

| RF (maximum input level)      | -10 | -5  | -   | dBm  |

### 12.3 Input/output terminal characteristics

Always comply with the stated values when attaching external components to the CSRB31024 LGA.

**NOTE** Current drawn by a pin is positive (+), current supplied is negative (-).

### 12.3.1 Switch-mode regulator

CSRB31024 LGA power supply rails are generated from a single pin connection to the battery, VDD\_BAT. Minimum decoupling should be 4.7 µF using the same low ESR components as the output capacitors.

For supplies that have high resistance (greater than 30  $\Omega$ ), such as CR2032 coin cells, large value decoupling may be used. When powered from high impedance sources, while CSRB31024 LGA changes operational modes, 22  $\mu$ F can significantly reduce voltage variation on VDD\_BAT.

The outputs of the Switch-mode Regulator require adequate decoupling. 4.7  $\mu$ F components are recommended, in order that a real capacitance of 3  $\mu$ F is presented to the chip based on a DC bias voltage derating of 3  $V_{DC}$  with AC200 mVrms.

**NOTE** Specifically 0402 components are not acceptable; PCB layout should use 0603 footprints. The component BOM should call for capacitors with a body thickness >0.65 mm.

Both the capacitance and ESR lead to observed output ripple:

A suitable ESR at 1 MHz should be under 0.10 Ω.

All power is delivered through the 2.2 µH power inductor. To achieve good stability and efficiency use:

- Saturation current (I<sub>sat</sub>) of more than 800 mA