# Qualcomm<sup>®</sup> Hexagon™ V71

# Programmer's Reference Manual

80-N2040-51 Rev. AB August 17, 2023

All Qualcomm products mentioned herein are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

Qualcomm and Hexagon are trademarks or registered trademarks of Qualcomm Incorporated. Other product and brand names may be trademarks or registered trademarks of their respective owners.

This technical data may be subject to U.S. and international export, re-export, or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

Qualcomm Technologies, Inc. 5775 Morehouse Drive San Diego, CA 92121 U.S.A.

# Contents

| Figures                             | 13 |

|-------------------------------------|----|

| Tables                              | 14 |

|                                     |    |

| 1 Introduction                      | 16 |

| 1.1 Conventions                     | 16 |

| 1.2 Technical assistance            | 16 |

| 2 Registers                         | 17 |

| 2.1 Register operands               | 17 |

| 2.2 General registers               | 19 |

| 2.3 Control registers               |    |

| 2.3.1 Program counter               | 23 |

| 2.3.2 Loop registers                | 23 |

| 2.3.3 User status register          | 24 |

| 2.3.4 Modifier registers            | 26 |

| 2.3.5 Predicate registers           | 27 |

| 2.3.6 Circular start registers      | 28 |

| 2.3.7 User general pointer register | 28 |

| 2.3.8 Global pointer                | 28 |

| 2.3.9 Cycle count registers         | 29 |

| 2.3.10 Frame limit register         | 29 |

| 2.3.11 Frame key register           | 29 |

| 2.3.12 Packet count registers       | 30 |

| 2.3.13 Qtimer registers             | 30 |

| 3 Instructions                      | 32 |

| 3.1 Instruction syntax              | 32 |

| 3.2 Instruction classes             | 35 |

| 3.3 Instruction packets             | 36 |

| 3.3.1 Packet execution semantics    | 37 |

| 3.3.2 Sequencing semantics          | 37 |

| 3.3.3 Resource constraints          | 38 |

| 3.3.4 Grouping constraints          | 39 |

| 3.3.5 Dependency constraints        | 40 |

| 3.3.6 Ordering constraints          | 40 |

|          | 3.3.7 Alignment constraints              | 41 |

|----------|------------------------------------------|----|

| 3.4      | Instruction intrinsics                   | 41 |

| 3.5      | Compound instructions                    | 42 |

| 3.6      | Duplex instructions                      | 42 |

|          |                                          |    |

| 4        | Data processing                          | 43 |

| 4.1      | Data types                               | 43 |

|          | 4.1.1 Fixed-point data                   | 43 |

|          | 4.1.2 Floating-point data                | 43 |

|          | 4.1.3 Complex data                       | 43 |

|          | 4.1.4 Vector data                        | 44 |

| 4.2      | Instruction options                      | 45 |

|          | 4.2.1 Fractional scaling                 | 45 |

|          | 4.2.2 Saturation                         | 46 |

|          | 4.2.3 Arithmetic rounding                | 46 |

|          | 4.2.4 Convergent rounding                | 46 |

|          | 4.2.5 Scaling for divide and square-root | 47 |

| 4.3      | XTYPE operations                         | 47 |

|          | 4.3.1 Floating point                     | 47 |

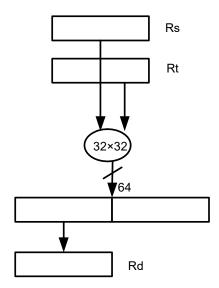

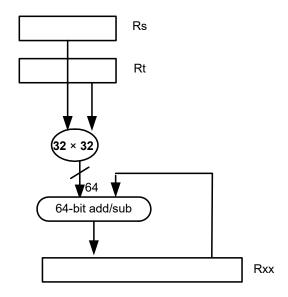

|          | 4.3.2 Multiply                           | 48 |

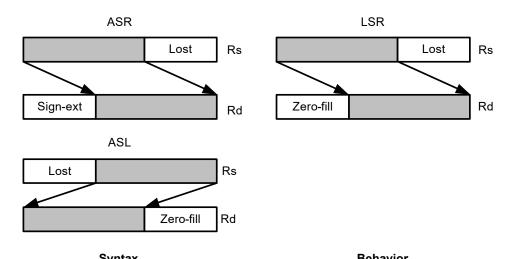

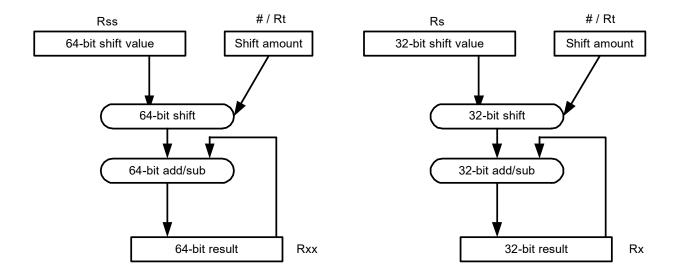

|          | 4.3.3 Shift                              | 50 |

| 4.4      | ALU32 operations                         | 51 |

| 4.5      | Vector operations                        | 51 |

| 4.6      | CR operations                            | 52 |

| 4.7      | Compound operations                      | 52 |

| 4.8      | Special operations                       | 53 |

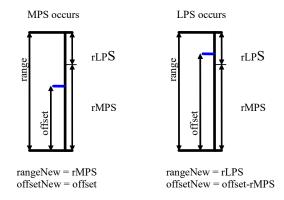

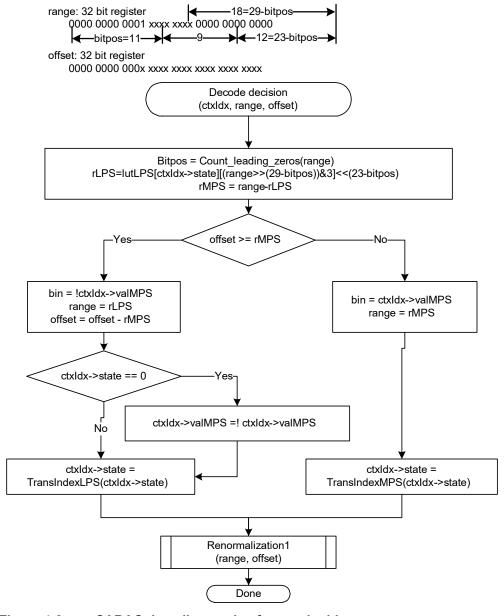

|          | 4.8.1 H.264 CABAC processing             | 53 |

|          | 4.8.1.1 CABAC implementation             | 54 |

|          | 4.8.1.2 Code example                     | 55 |

|          | 4.8.2 IP Internet checksum               | 56 |

|          | 4.8.2.1 Code example                     | 56 |

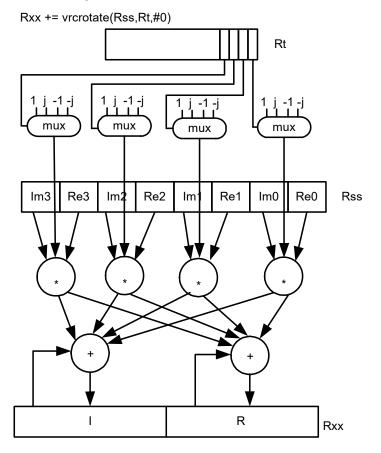

|          | 4.8.3 Software-defined radio             | 57 |

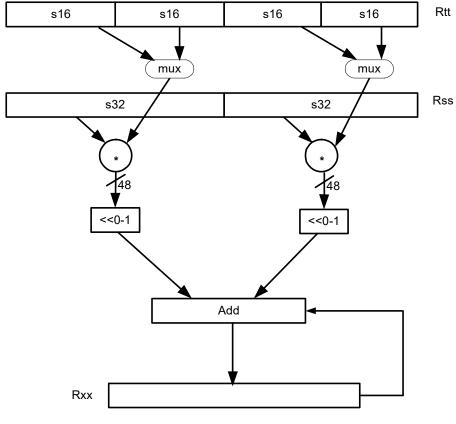

|          | 4.8.3.1 Rake despreading                 | 57 |

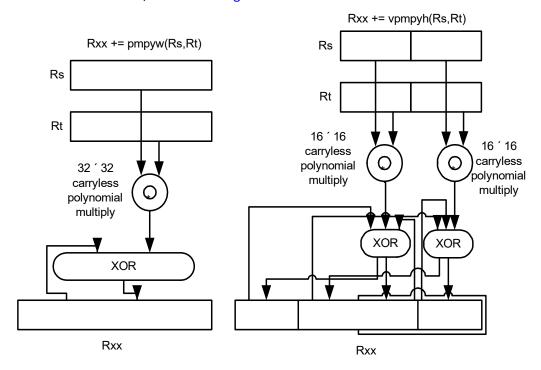

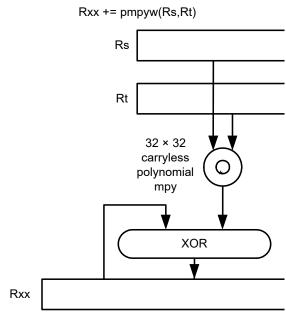

|          | 4.8.3.2 Polynomial operations            | 58 |

|          |                                          |    |

| <b>5</b> | Memory                                   | 60 |

| 5.1      | Memory model for the Hexagon processor   | 60 |

|          | 5.1.1 Address space                      | 60 |

|          | 5.1.2 Byte order                         |    |

|          | 5.1.3 Alignment                          | 61 |

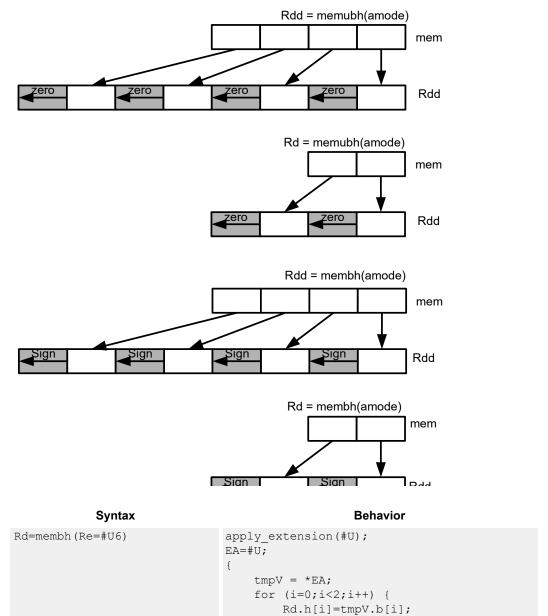

| 5.2      | Memory loads                             |    |

| 5.3      | Memory stores                            | 62 |

| 5.4  | Dual stores                                     | .63 |

|------|-------------------------------------------------|-----|

| 5.5  | Slot 1 store with slot 0 load                   | .63 |

| 5.6  | New-value stores                                | .63 |

| 5.7  | Mem-ops                                         | .64 |

| 5.8  | Addressing modes                                | .64 |

|      | 5.8.1 Absolute                                  | .65 |

|      | 5.8.2 Absolute-set                              | .65 |

|      | 5.8.3 Absolute with register offset             | .65 |

|      | 5.8.4 Global pointer relative                   | .66 |

|      | 5.8.5 Indirect                                  | .66 |

|      | 5.8.6 Indirect with offset                      | .67 |

|      | 5.8.7 Indirect with register offset             | .67 |

|      | 5.8.8 Indirect with autoincrement immediate     | .67 |

|      | 5.8.9 Indirect with autoincrement register      | .68 |

|      | 5.8.10 Circular with autoincrement immediate    | .68 |

|      | 5.8.11 Circular with autoincrement register     | .70 |

|      | 5.8.12 Bit-reversed with autoincrement register | .71 |

| 5.9  | Conditional load/stores                         | .72 |

| 5.10 | Cache memory                                    | .73 |

|      | 5.10.1 Uncached memory                          | .74 |

|      | 5.10.2 Tightly coupled memory                   | .74 |

|      | 5.10.3 Cache maintenance operations             | .74 |

|      | 5.10.4 L2 cache operations                      | .75 |

|      | 5.10.5 Cache line zero                          | .75 |

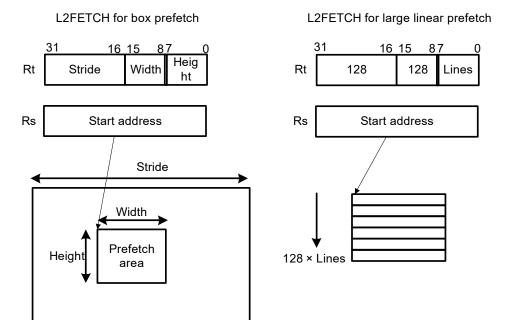

|      | 5.10.6 Cache prefetch                           | .76 |

| 5.1  | 1 Memory ordering                               | .79 |

| 5.1  | 2 Atomic operations                             | .80 |

|      |                                                 |     |

|      | Conditional execution                           |     |

| 6.1  | Scalar predicates                               |     |

|      | 6.1.1 Generating scalar predicates              |     |

|      | 6.1.2 Consuming scalar predicates               |     |

|      | 6.1.3 Auto-AND predicates                       |     |

|      | 6.1.4 Dot-new predicates                        | .86 |

|      | 6.1.5 Dependency constraints                    |     |

| 6.2  | Vector predicates                               | .87 |

|      | 6.2.1 Vector compare                            | .88 |

|      | 6.2.2 Vector mux instruction                    |     |

|      | 6.2.3 Using vector conditionals                 | .89 |

| 6.3  | Predicate operations                            | .90 |

| 7 Software stack                   | 91  |

|------------------------------------|-----|

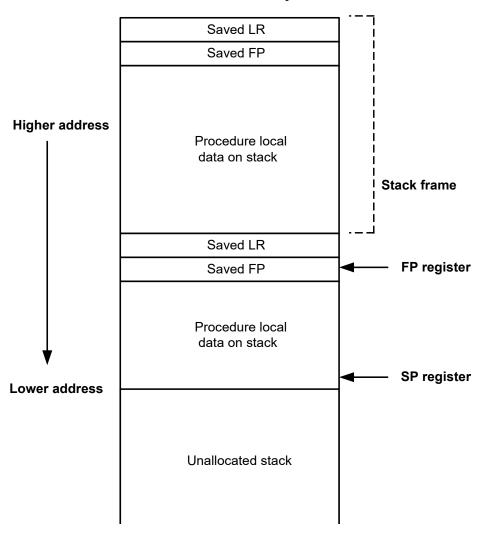

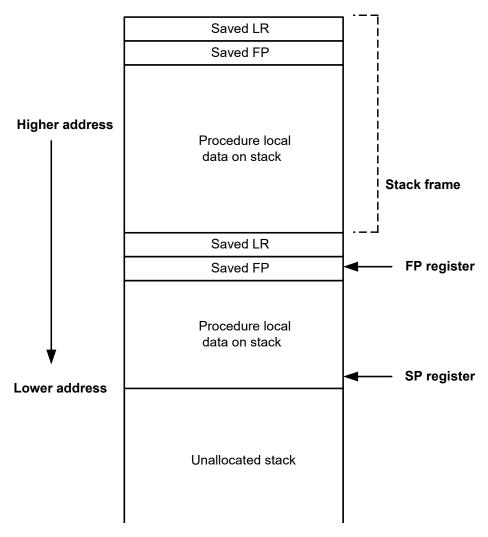

| 7.1 Stack structure                | 91  |

| 7.2 Stack frames                   | 92  |

| 7.3 Stack protection               | 92  |

| 7.3.1 Stack bounds checking        | 92  |

| 7.3.2 Stack smashing protection    | 93  |

| 7.4 Stack registers                | 93  |

| 7.5 Stack instructions             | 93  |

| 8 Program flow                     | 95  |

| 8.1 Conditional instructions       | 95  |

| 8.2 Hardware loops                 | 96  |

| 8.2.1 Loop setup                   | 97  |

| 8.2.2 Loop end                     | 98  |

| 8.2.3 Loop execution               | 99  |

| 8.2.4 Pipelined hardware loops     | 99  |

| 8.2.5 Loop restrictions            | 102 |

| 8.3 Software branches              | 102 |

| 8.3.1 Jumps                        | 103 |

| 8.3.2 Calls                        | 103 |

| 8.3.3 Returns                      | 104 |

| 8.3.4 Extended branches            | 105 |

| 8.3.5 Branches to and from packets | 105 |

| 8.4 Speculative jumps              | 105 |

| 8.5 Compare jumps                  | 107 |

| 8.5.1 New-value compare jumps      | 107 |

| 8.6 Register transfer jumps        | 109 |

| 8.7 Dual jumps                     | 109 |

| 8.8 Hint indirect jump target      | 110 |

| 8.9 Pauses                         |     |

| 8.10 Exceptions                    | 111 |

| 9 PMU events                       | 114 |

| 9.1 V71 processor event symbols    | 114 |

| 10 Instruction encoding            | 122 |

| 10.1 Instructions                  |     |

| 10.2 Sub-instructions              |     |

| 10.3 Duplexes                      |     |

| 10.4 Instruction classes           |     |

| 10.5 Instruction packets           |     |

| 10.6 Loop packets                  |     |

| 10.7 Immediate values            | 130 |

|----------------------------------|-----|

| 10.8 Scaled immediate values     | 131 |

| 10.9 Constant extenders          | 131 |

| 10.10 New-value operands         | 135 |

| 10.11 Instruction mapping        | 135 |

| 11 Instruction set               | 136 |

| 11.1 ALU32                       |     |

| 11.1.1 ALU32 ALU                 |     |

| Add                              |     |

| Logical operations               |     |

| Negate                           |     |

| Nop                              |     |

| Subtract                         |     |

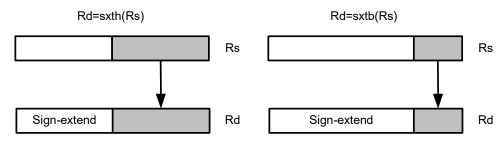

| Sign extend                      |     |

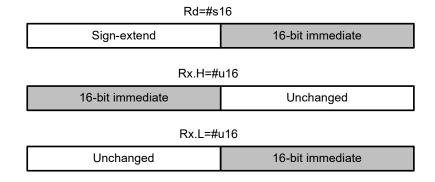

| Transfer immediate               |     |

| Transfer register                |     |

| Vector add halfwords             |     |

| Vector average halfwords         |     |

| Vector subtract halfwords        |     |

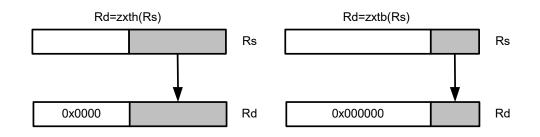

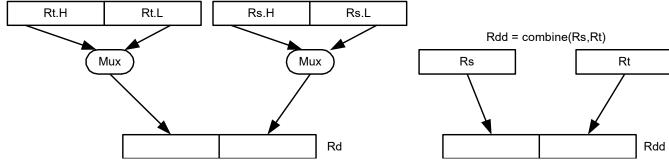

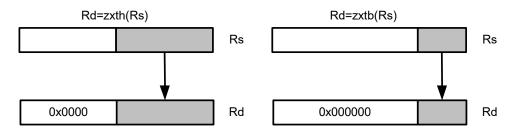

| Zero extend                      | 151 |

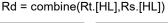

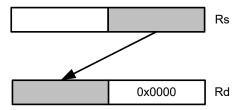

| 11.1.2 ALU32 PERM                | 152 |

| Combine words into doubleword    | 152 |

| Mux                              | 154 |

| Shift word by 16                 | 156 |

| Pack high and low halfwords      | 157 |

| 11.1.3 ALU32 PRED                | 158 |

| Conditional add                  | 158 |

| Conditional shift halfword       | 160 |

| Conditional combine              | 162 |

| Conditional logical operations   | 163 |

| Conditional subtract             | 165 |

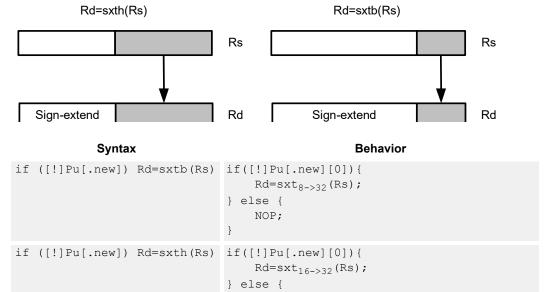

| Conditional sign extend          | 166 |

| Conditional transfer             | 167 |

| Conditional zero extend          | 168 |

| Compare                          | 169 |

| Compare to general register      | 171 |

| 11.2 CR                          | 172 |

| End loop instructions            | 172 |

| Corner detection acceleration    | 173 |

| Logical reductions on predicates | 174 |

| Looping instructions             | 175 |

| Add to PC                        | 177 |

|         | Pipelined loop instructions                     | 178 |     |

|---------|-------------------------------------------------|-----|-----|

|         | Logical operations on predicates                | 180 |     |

|         | User control register transfer                  | 182 |     |

| 11.3 JR |                                                 |     | 183 |

|         | Call subroutine from register                   | 183 |     |

|         | Hint an indirect jump address                   | 184 |     |

|         | Jump to address from register                   | 185 |     |

| 11.4 J  |                                                 |     | 186 |

|         | Call subroutine                                 | 186 |     |

|         | Compare and jump                                | 188 |     |

|         | Jump to address                                 | 192 |     |

|         | Jump to address conditioned on new predicate    | 193 |     |

|         | Jump to address condition on register value     | 194 |     |

|         | Transfer and jump                               | 196 |     |

| 11.5 LD |                                                 |     | 197 |

|         | Load doubleword                                 | 197 |     |

|         | Load-acquire doubleword                         | 199 |     |

|         | Load doubleword conditionally                   | 200 |     |

|         | Load byte                                       | 202 |     |

|         | Load byte conditionally                         | 204 |     |

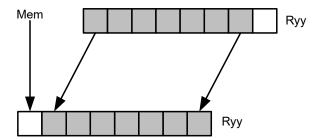

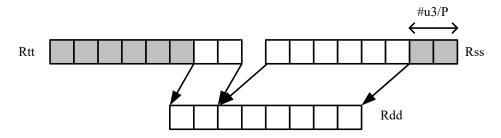

|         | Load byte into shifted vector                   | 206 |     |

|         | Load half into shifted vector                   | 209 |     |

|         | Load halfword                                   | 212 |     |

|         | Load halfword conditionally                     | 214 |     |

|         | Memory copy                                     | 216 |     |

|         | Load unsigned byte                              | 217 |     |

|         | Load unsigned byte conditionally                | 219 |     |

|         | Load unsigned halfword                          | 221 |     |

|         | Load unsigned halfword conditionally            | 223 |     |

|         | Load word                                       | 225 |     |

|         | Load-acquire word                               | 227 |     |

|         | Load word conditionally                         | 228 |     |

|         | Deallocate stack frame                          | 230 |     |

|         | Deallocate frame and return                     | 232 |     |

|         | Load and unpack bytes to halfwords              | 234 |     |

| 11.6 ME | MOP                                             |     | 242 |

|         | Operation on memory byte                        | 242 |     |

|         | Operation on memory halfword                    | 244 |     |

|         | Operation on memory word                        | 245 |     |

| 11.7 NV | ·                                               |     | 246 |

| 11.7    | .1 NV J                                         |     | 246 |

|         | Jump to address condition on new register value | 246 |     |

| 11.7    | .2 NV ST                                        |     | 250 |

| Store new-value byte                          | 250 |

|-----------------------------------------------|-----|

| Store new-value byte conditionally            | 252 |

| Store new-value halfword                      | 254 |

| Store new-value halfword conditionally        | 256 |

| Store new-value word                          | 258 |

| Store new-value word conditionally            | 260 |

| 11.8 ST                                       | 262 |

| Store doubleword                              | 262 |

| Store-release doubleword                      | 264 |

| Store doubleword conditionally                | 265 |

| Store byte                                    | 267 |

| Store byte conditionally                      | 269 |

| Store halfword                                | 271 |

| Store halfword conditionally                  | 274 |

| Release                                       | 277 |

| Store word                                    | 278 |

| Store-release word                            | 280 |

| Store word conditionally                      | 281 |

| Allocate stack frame                          | 283 |

| 11.9 SYSTEM                                   | 285 |

| 11.9.1 SYSTEM USER                            | 285 |

| Load locked                                   | 285 |

| Store conditional                             | 286 |

| Zero a cache line                             | 287 |

| Memory barrier                                | 288 |

| Breakpoint                                    |     |

| Data cache prefetch                           | 290 |

| Data cache maintenance user operations        | 291 |

| Send value to DIAG trace                      | 293 |

| Instruction cache maintenance user operations | 294 |

| Instruction synchronization                   | 295 |

| L2 cache prefetch                             | 296 |

| Pause                                         | 298 |

| Memory thread synchronization                 | 299 |

| Send value to ETM trace                       | 300 |

| Trap                                          | 301 |

| 11.10 XTYPE                                   | 302 |

| 11.10.1 XTYPE ALU                             |     |

| Absolute value doubleword                     | 302 |

| Absolute value word                           | 303 |

| Add and accumulate                            | 304 |

| Add doublewords                               | 306 |

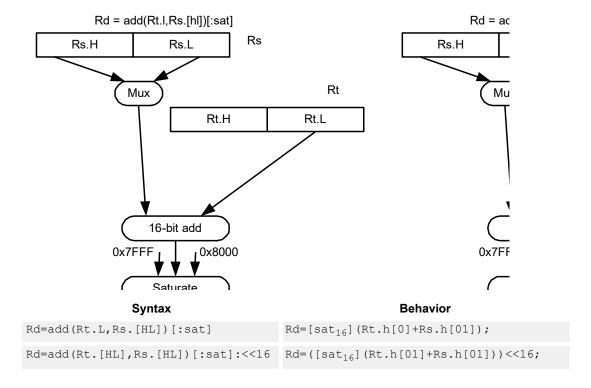

| Add halfword                                  | 308 |

| Add or subtract doublewords with carry                        | 310 |

|---------------------------------------------------------------|-----|

| Clip to unsigned                                              | 311 |

| Logical doublewords                                           | 312 |

| Logical-logical doublewords                                   | 313 |

| Logical-logical words                                         | 314 |

| Maximum words                                                 | 316 |

| Maximum doublewords                                           | 317 |

| Minimum words                                                 | 318 |

| Minimum doublewords                                           | 319 |

| Modulo wrap                                                   | 320 |

| Negate                                                        | 321 |

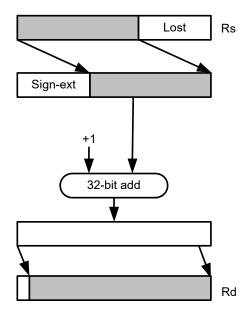

| Round                                                         | 322 |

| Subtract doublewords                                          | 325 |

| Subtract and accumulate words                                 | 326 |

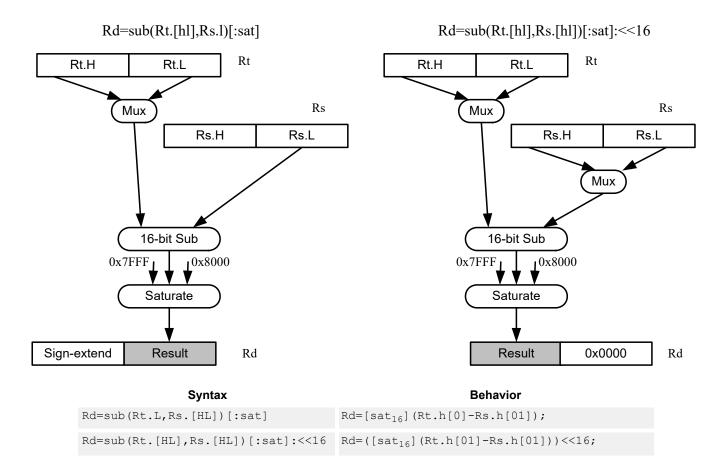

| Subtract halfword                                             | 327 |

| Sign extend word to doubleword                                | 329 |

| Vector absolute value halfwords                               | 330 |

| Vector absolute value words                                   | 331 |

| Vector absolute difference bytes                              | 332 |

| Vector absolute difference halfwords                          | 333 |

| Vector absolute difference words                              | 334 |

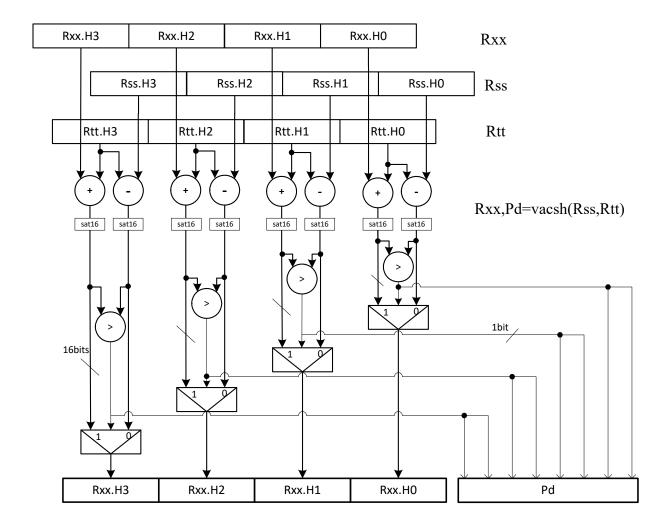

| Vector add compare and select maximum bytes                   | 335 |

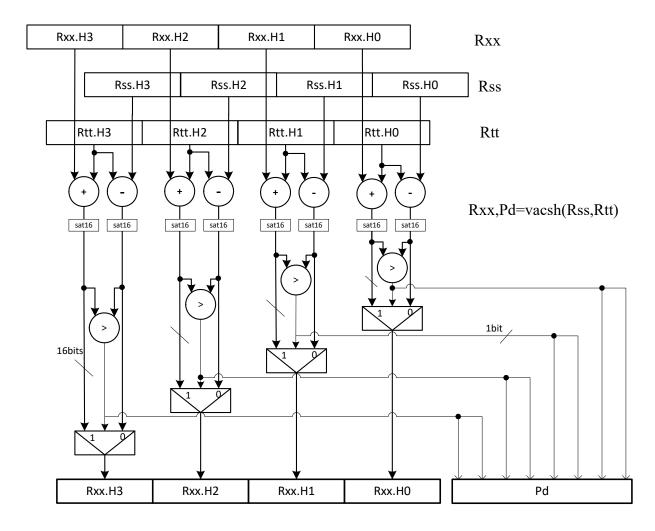

| Vector add compare and select maximum halfwords               | 336 |

| Vector add halfwords                                          | 338 |

| Vector add halfwords with saturate and pack to unsigned bytes | 339 |

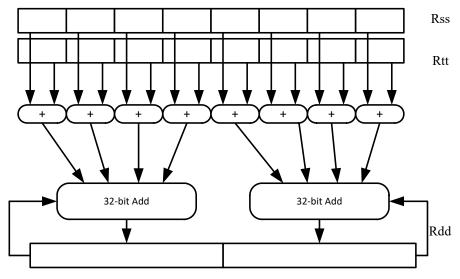

| Vector reduce add unsigned bytes                              | 340 |

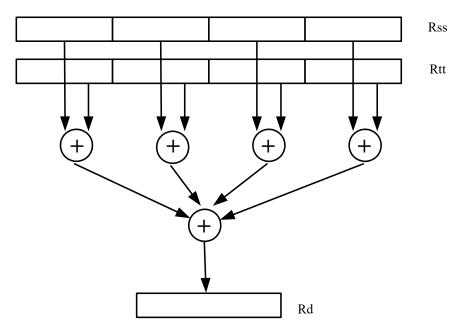

| Vector reduce add halfwords                                   | 342 |

| Vector add bytes                                              | 344 |

| Vector add words                                              | 345 |

| Vector average halfwords                                      | 346 |

| Vector average unsigned bytes                                 | 348 |

| Vector average words                                          | 349 |

| Vector clip to unsigned                                       | 351 |

| Vector conditional negate                                     | 352 |

| Vector maximum bytes                                          | 353 |

| Vector maximum halfwords                                      | 354 |

| Vector reduce maximum halfwords                               | 355 |

| Vector reduce maximum words                                   | 357 |

| Vector maximum words                                          | 358 |

| Vector minimum bytes                                          | 359 |

| Vector minimum halfwords                                      | 360 |

| Vector reduce minimum halfwords                               | 361 |

| Vector reduce minimum words                                   | 363 |

| Vector minimum words                                         | 365 |     |

|--------------------------------------------------------------|-----|-----|

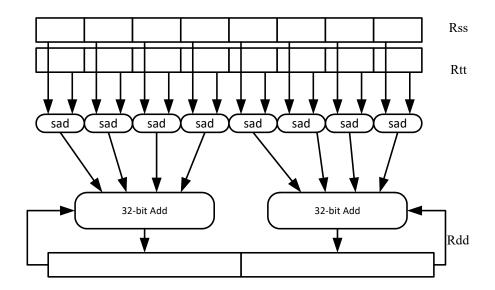

| Vector sum of absolute differences unsigned bytes            | 366 |     |

| Vector subtract halfwords                                    | 368 |     |

| Vector subtract bytes                                        | 369 |     |

| Vector subtract words                                        | 370 |     |

| 11.10.2 XTYPE BIT                                            |     | 371 |

| Count leading                                                | 371 |     |

| Count population                                             | 373 |     |

| Count trailing                                               | 374 |     |

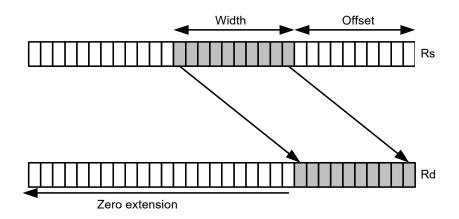

| Extract bit field                                            | 375 |     |

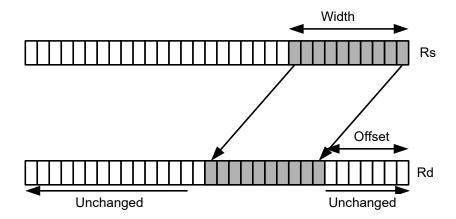

| Insert bit field                                             | 378 |     |

| Interleave/deinterleave                                      | 380 |     |

| Linear feedback-shift iteration                              | 381 |     |

| Masked parity                                                | 382 |     |

| Bit reverse                                                  | 383 |     |

| Set/clear/toggle bit                                         | 384 |     |

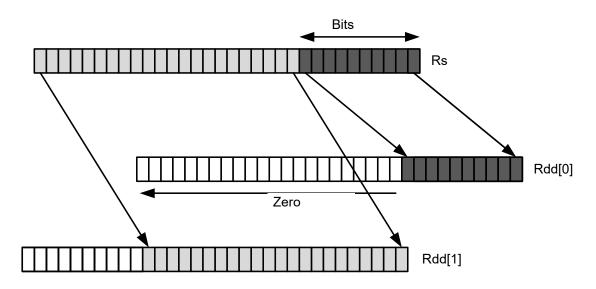

| Split bit field                                              | 386 |     |

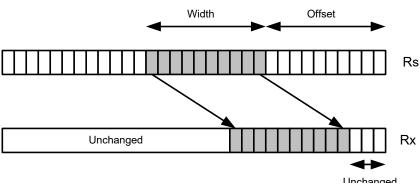

| Table index                                                  | 388 |     |

| 11.10.3 XTYPE COMPLEX                                        |     | 390 |

| Complex add/sub halfwords                                    | 390 |     |

| Complex add/sub words                                        | 393 |     |

| Complex multiply                                             | 395 |     |

| Complex multiply real or imaginary                           | 398 |     |

| Complex multiply with round and pack                         | 400 |     |

| Complex multiply 32 x 16                                     | 402 |     |

| Complex multiply real or imaginary 32-bit                    | 404 |     |

| Vector complex multiply real or imaginary                    | 408 |     |

| Vector complex conjugate                                     | 411 |     |

| Vector complex rotate                                        | 412 |     |

| Vector reduce complex multiply by scalar                     | 414 |     |

| Vector reduce complex multiply by scalar with round and pack | 417 |     |

| Vector reduce complex rotate                                 | 419 |     |

| 11.10.4 XTYPE FP                                             |     | 422 |

| Floating point addition                                      | 422 |     |

| Classify floating-point value                                | 423 |     |

| Compare floating-point value                                 | 424 |     |

| Convert floating-point value to other format                 | 426 |     |

| Convert integer to floating-point value                      | 427 |     |

| Convert floating-point value to integer                      |     |     |

| Floating point extreme value assistance                      | 431 |     |

| Floating point fused multiply-add                            | 432 |     |

| Floating point fused multiply-add with scaling               | 433 |     |

| Floating point reciprocal square root approximation          | 434 |     |

| Floating point fused multiply-add for library routines | 435 |

|--------------------------------------------------------|-----|

| Create floating-point constant                         | 437 |

| Floating point maximum                                 | 438 |

| Floating point minimum                                 | 439 |

| Floating point multiply                                | 440 |

| Floating point reciprocal approximation                | 441 |

| Floating point subtraction                             | 442 |

| 11.10.5 XTYPE MPY                                      | 443 |

| Multiply and use lower result                          | 443 |

| Vector multiply word by signed half (32×16)            | 446 |

| Vector multiply word by unsigned half (32×16)          | 450 |

| Multiply signed halfwords                              | 454 |

| Multiply unsigned halfwords                            | 461 |

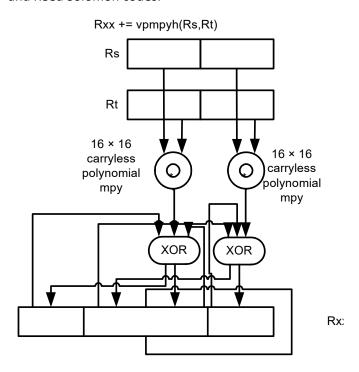

| Polynomial multiply words                              | 465 |

| Vector reduce multiply word by signed half (32×16)     | 467 |

| Multiply and use upper result                          | 469 |

| Multiply and use full result                           | 471 |

| Vector dual multiply                                   | 473 |

| Vector dual multiply with round and pack               | 475 |

| Vector reduce multiply bytes                           | 477 |

| Vector dual multiply signed by unsigned bytes          | 479 |

| Vector multiply even halfwords                         | 481 |

| Vector multiply halfwords                              | 483 |

| Vector multiply halfwords with round and pack          | 485 |

| Vector multiply halfwords, signed by unsigned          | 487 |

| Vector reduce multiply halfwords                       | 488 |

| Vector multiply bytes                                  | 490 |

| Vector polynomial multiply halfwords                   | 492 |

| 11.10.6 XTYPE PERM                                     | 494 |

| CABAC decode bin                                       | 494 |

| Saturate                                               | 496 |

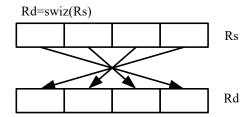

| Swizzle bytes                                          | 498 |

| Vector align                                           | 499 |

| Vector round and pack                                  | 500 |

| Vector saturate and pack                               | 502 |

| Vector saturate without pack                           | 504 |

| Vector shuffle                                         | 506 |

| Vector splat bytes                                     | 508 |

| Vector splat halfwords                                 | 509 |

| Vector splice                                          | 510 |

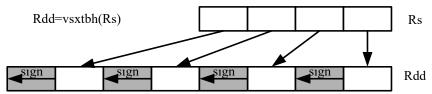

| Vector sign extend                                     | 511 |

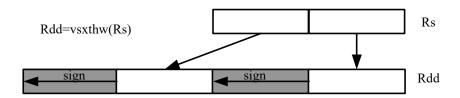

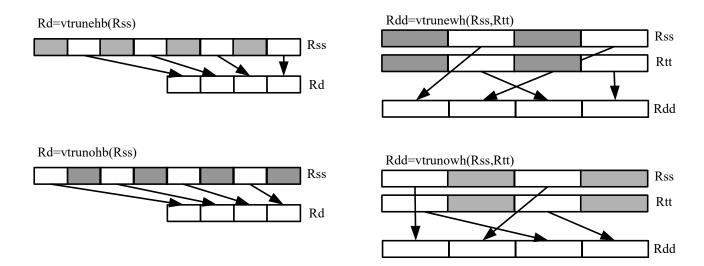

| Vector truncate                                        | 513 |

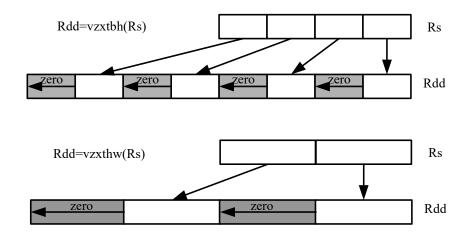

| Vector zero extend                                     | 515 |

| 11.10 | .7 XTYPE PRED                                            |     | .517 |

|-------|----------------------------------------------------------|-----|------|

|       | Bounds check                                             | 517 |      |

|       | Compare byte                                             | 518 |      |

|       | Compare half                                             | 520 |      |

|       | Compare doublewords                                      | 522 |      |

|       | Compare bit mask                                         | 523 |      |

|       | Mask generate from predicate                             | 524 |      |

|       | Check for TLB match                                      | 525 |      |

|       | Predicate transfer                                       | 526 |      |

|       | Test bit                                                 | 527 |      |

|       | Vector compare halfwords                                 | 528 |      |

|       | Vector compare bytes for any match                       | 530 |      |

|       | Vector compare bytes                                     | 531 |      |

|       | Vector compare words                                     | 533 |      |

|       | Viterbi pack even and odd predicate bits                 | 535 |      |

|       | Vector mux                                               | 536 |      |

| 11.10 | .8 XTYPE SHIFT                                           |     | .537 |

|       | Mask generate from immediate                             | 537 |      |

|       | Shift by immediate                                       | 538 |      |

|       | Shift by immediate and accumulate                        | 540 |      |

|       | Shift by immediate and add                               | 543 |      |

|       | Shift by immediate and logical                           | 544 |      |

|       | Shift right by immediate with rounding                   | 548 |      |

|       | Shift left by immediate with saturation                  | 550 |      |

|       | Shift by register                                        | 551 |      |

|       | Shift by register and accumulate                         | 553 |      |

|       | Shift by register and logical                            | 556 |      |

|       | Shift by register with saturation                        | 559 |      |

|       | Vector shift halfwords by immediate                      | 560 |      |

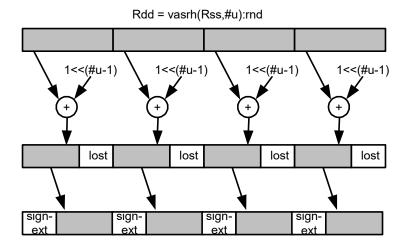

|       | Vector arithmetic shift halfwords with round             | 561 |      |

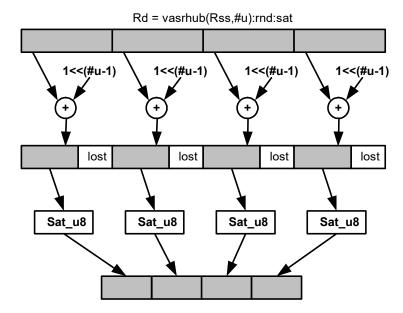

|       | Vector arithmetic shift halfwords with saturate and pack | 562 |      |

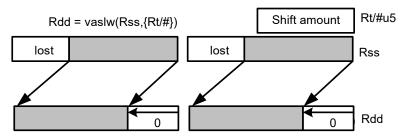

|       | Vector shift halfwords by register                       | 564 |      |

|       | Vector shift words by immediate                          | 566 |      |

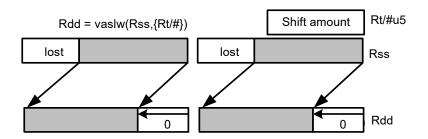

|       | Vector shift words by register                           | 567 |      |

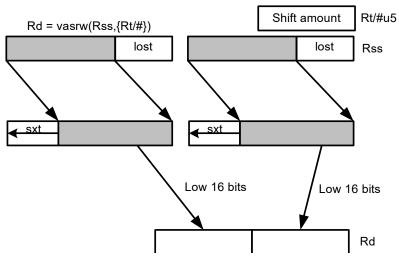

|       | Vector shift words with truncate and pack                | 569 |      |

12

# **Figures**

| Figure 1-1  | Hexagon V71 processor architecture   | 19  |

|-------------|--------------------------------------|-----|

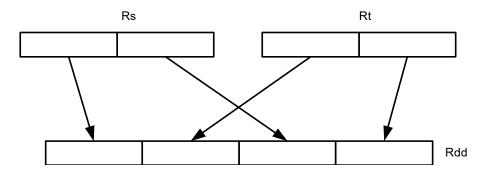

| Figure 1-2  | Vector instruction example           | 23  |

| Figure 1-3  | Instruction classes and combinations |     |

| Figure 1-4  | Register field symbols               | 29  |

| Figure 2-1  | General registers                    |     |

| Figure 2-2  | Control registers                    |     |

| Figure 3-1  | Packet grouping combinations         | 51  |

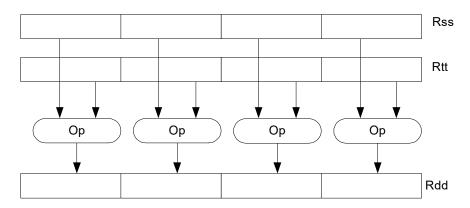

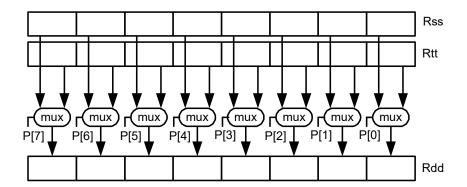

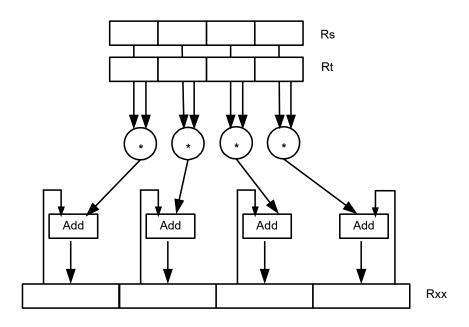

| Figure 4-1  | Vector byte operation                | 58  |

| Figure 4-2  | Vector halfword operation            | 58  |

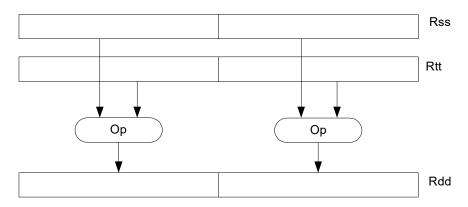

| Figure 4-3  | Vector word operation                | 58  |

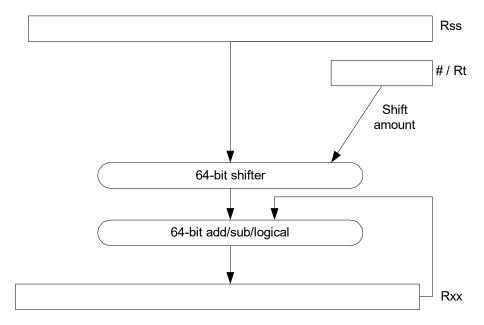

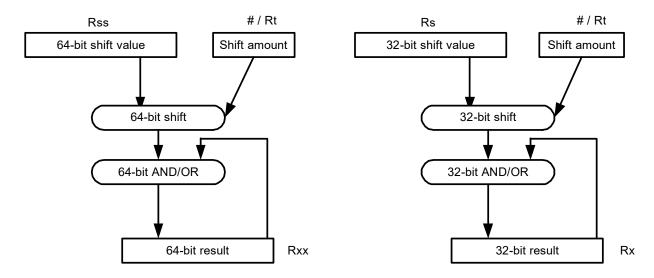

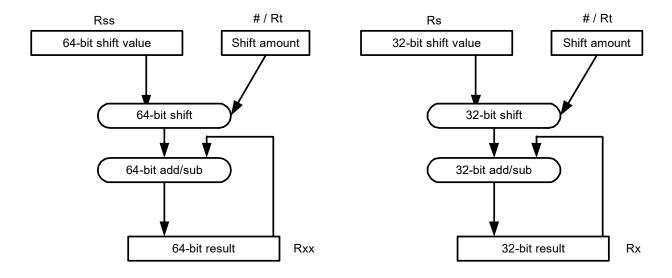

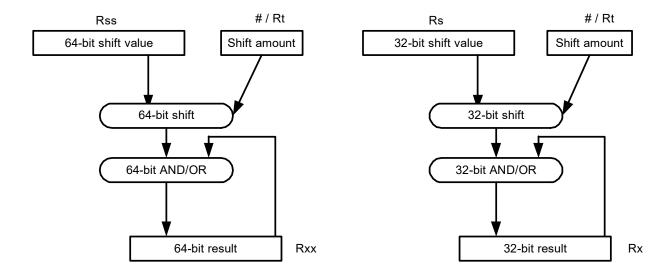

| Figure 4-4  | 64-bit shift and add/sub/logical     | 67  |

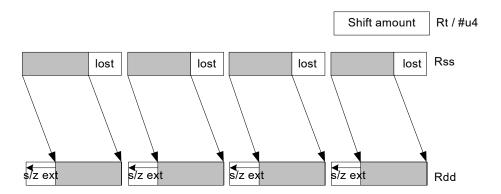

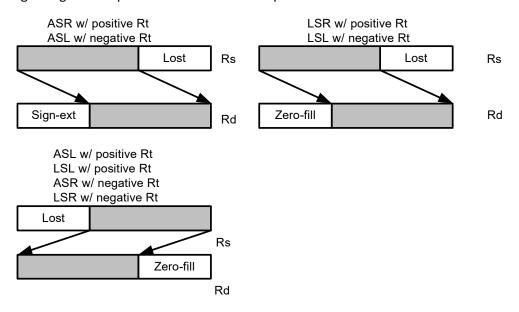

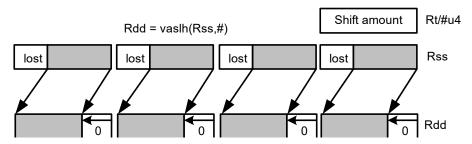

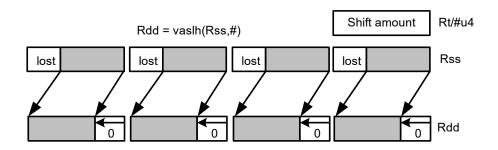

| Figure 4-5  | Vector halfword shift right          | 70  |

| Figure 5-1  | Hexagon processor byte order         | 80  |

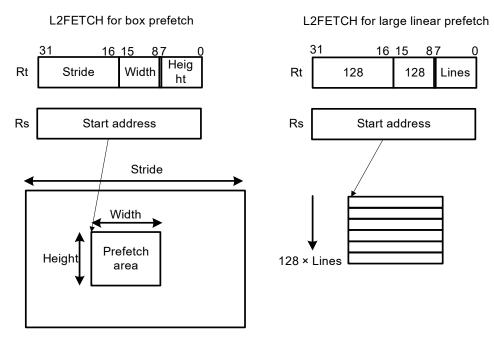

| Figure 5-2  | L2fetch instruction                  | 99  |

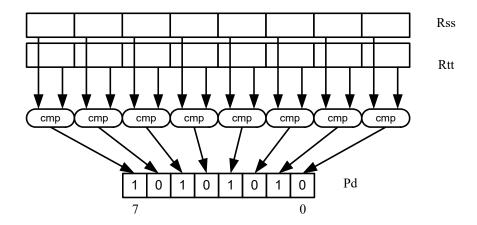

| Figure 6-1  | Vector byte compare                  | 110 |

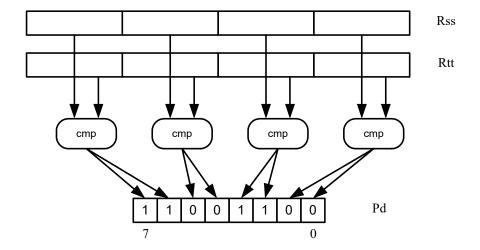

| Figure 6-2  | Vector halfword compare              | 110 |

| Figure 6-3  | Vector mux instruction.              | 111 |

| Figure 7-1  | Stack structure                      | 115 |

| Figure 10-1 | Instruction packet encoding          | 158 |

# **Tables**

| Table 1-1  | Register symbols                                        | . 28 |

|------------|---------------------------------------------------------|------|

| Table 1-2  | Register bit field symbols                              | . 29 |

| Table 1-3  | Instruction operands                                    | .30  |

| Table 1-4  | Data symbols.                                           | .31  |

| Table 2-1  | General register aliases                                | .34  |

| Table 2-2  | General register pairs                                  | .34  |

| Table 2-3  | Aliased control registers                               | .36  |

| Table 2-4  | Control register pairs                                  | .37  |

| Table 2-5  | Loop registers                                          | .38  |

| Table 2-6  | User status register                                    | .39  |

| Table 2-7  | Modifier registers (indirect auto-increment addressing) | .41  |

| Table 2-8  | Modifier registers (circular addressing)                | .41  |

| Table 2-9  | Modifier registers (bit-reversed addressing)            | .42  |

| Table 2-10 | Predicate registers                                     | .42  |

| Table 2-11 | Circular start registers                                | .43  |

| Table 2-12 | User general pointer register                           | .43  |

| Table 2-13 | Global pointer register                                 | .43  |

| Table 2-14 | Cycle count registers                                   | .44  |

| Table 2-15 | Frame limit register                                    | .44  |

| Table 2-16 | Frame key register                                      | .45  |

| Table 2-17 | Packet count registers                                  | .45  |

| Table 2-18 | Qtimer registers                                        | .46  |

| Table 3-1  | Instruction symbols                                     | .47  |

| Table 3-2  | Instruction classes                                     | .48  |

| Table 4-1  | Single-precision multiply options                       | .65  |

| Table 4-2  | Double precision multiply options                       | .65  |

| Table 4-3  | Control register transfer instructions                  | .71  |

| Table 5-1  | Memory alignment restrictions                           | .81  |

| Table 5-2  | Load instructions                                       | .81  |

| Table 5-3  | Store instructions                                      | .82  |

| Table 5-4  | Mem-ops                                                 | .84  |

| Table 5-5  | Addressing modes                                        | .84  |

| Table 5-6  | Offset ranges (global pointer relative)                 | .86  |

| Table 5-7  | Offset ranges (indirect with offset)                    | .87  |

| Table 5-8  | Increment ranges (indirect with auto-inc immediate)     | .88  |

| Table 5-9  | Increment ranges (circular with auto-inc immediate)     | .89  |

| Table 5-10 | Increment ranges (circular with auto-inc register)      | .91  |

| Table 5-11 | Addressing modes (conditional load/store)               | .93  |

| Table 5-12 | Conditional offset ranges (indirect with offset)        | .94  |

| Table 5-13 | Cache instructions (user-level)                         | .96  |

| Table 5-14 | Memory ordering instructions                            | 100  |

| Table 5-15  | Atomic instructions                          | 101 |

|-------------|----------------------------------------------|-----|

| Table 6-1   | Scalar predicate-generating instructions     | 104 |

| Table 6-2   | Vector mux instruction                       | 111 |

| Table 6-3   | Predicate register instructions              | 113 |

| Table 7-1   | Stack registers                              | 117 |

| Table 7-2   | Stack instructions                           | 118 |

| Table 8-1   | Loop instructions                            | 121 |

| Table 8-2   | Software pipelined loop                      | 125 |

| Table 8-3   | Software pipelined loop (using spNloop0)     | 126 |

| Table 8-4   | Software branch instructions                 | 127 |

| Table 8-5   | Jump instructions                            | 128 |

| Table 8-6   | Call instructions                            | 128 |

| Table 8-7   | Return instructions                          | 129 |

| Table 8-8   | Speculative jump instructions                | 131 |

| Table 8-9   | Compare jump instructions                    | 133 |

| Table 8-10  | New-value compare jump instructions          | 134 |

| Table 8-11  | Register transfer jump instructions          | 135 |

| Table 8-12  | Dual jump instructions                       | 135 |

| Table 8-13  | Jump hint instruction                        | 136 |

| Table 8-14  | Pause instruction                            | 137 |

| Table 8-15  | V71 exceptions                               | 138 |

| Table 9-1   | V71 processor events symbols                 | 141 |

| Table 10-1  | Instruction fields                           | 151 |

| Table 10-2  | Sub-instructions                             | 153 |

| Table 10-3  | Sub-instruction registers                    | 154 |

| Table 10-4  | Duplex instruction                           | 155 |

| Table 10-5  | Duplex ICLASS field                          | 155 |

| Table 10-6  | Instruction class encoding                   | 157 |

| Table 10-7  | Loop packet encoding                         | 159 |

| Table 10-8  | Scaled immediate encoding (indirect offsets) | 160 |

| Table 10-9  | Constant extender encoding                   | 161 |

| Table 10-10 | Constant extender instructions               | 162 |

| Table 10-11 | Instruction mapping                          | 165 |

| Table 11-1  | Instruction operand symbols                  | 166 |

| Table 11-2  | Instruction behavior symbols                 | 167 |

# 1 Introduction

The Qualcomm Hexagon™ processor is a general-purpose digital signal processor designed for high performance and low power across a wide variety of multimedia and modem applications. V71 is a member of the sixth generation of the Hexagon processor architecture.

### 1.1 Conventions

Courier new font is used for computer text and code samples, for example, hexagon <function name>().

The following notation is used to define command syntax:

- Square brackets enclose optional items, for example, [label].

- **Bold** indicates literal symbols for example, [comment].

- The vertical bar character, |, indicates a choice of items.

- Parentheses enclose a choice of items for example, (add|del).

- An ellipsis, . . . , follows items that can appear more than once.

### 1.2 Technical assistance

For assistance or clarification on information in this document, submit a case to Qualcomm Technologies, Inc. (QTI) at https://createpoint.qti.qualco For assistance or clarification on information in this document, open a technical support case at https://support.qualcomm.com/.

You will need to register for a Qualcomm ID account and your company must have support enabled to access our Case system.

Other systems and support resources are listed on https://qualcomm.com/support.

If you need further assistance, you can send an email to qualcomm.support@qti.qualcomm.com.

# 2 Registers

The Hexagon processor has two sets of registers:

- General registers are for general-purpose computation including address generation and scalar and vector arithmetic.

- Control registers support special-purpose processor features such as hardware loops and predicates.

# 2.1 Register operands

The following notation describes register operands in the syntax and behavior of instructions:

```

Rds[.elst]

```

The ds field indicates the register operand type and bit size (as defined in Table 2-1).

Table 2-1 Register symbols

| Symbol | Operand type           | Size (in bits) |

|--------|------------------------|----------------|

| d      | Destination            | 32             |

| dd     |                        | 64             |

| s      | First source           | 32             |

| ss     |                        | 64             |

| t      | Second source          | 32             |

| tt     |                        | 64             |

| u      | Third source           | 32             |

| uu     |                        | 64             |

| х      | Source and destination | 32             |

| xx     |                        | 64             |

Examples of ds field (describing instruction syntax):

Examples of ds field (describing instruction behavior):

```

Rdd = Rss + Rtt // Rdd, Rss, Rtt -> 64-bit registers

```

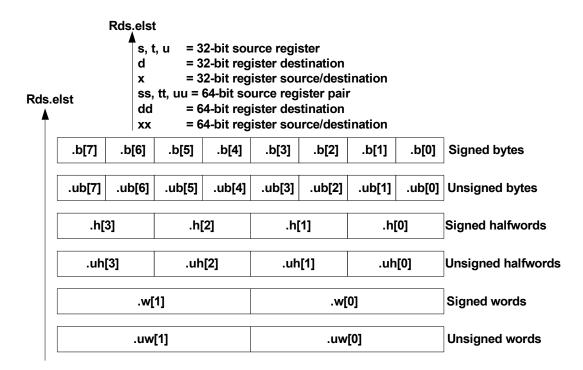

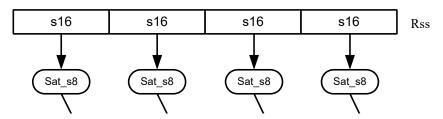

The optional elst field (short for element size and type) specifies parts of a register when the register is used as a vector. It can specify the following values:

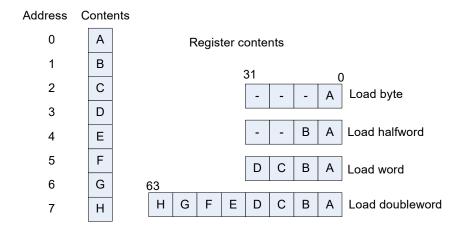

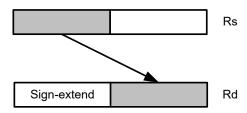

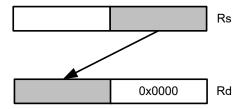

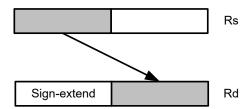

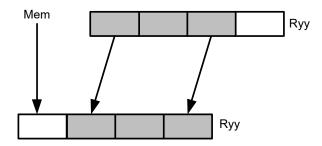

- A signed or unsigned byte, halfword, or word within the register (as defined in Figure 2-1)

- A bit field within the register (as defined in Table 2-2).

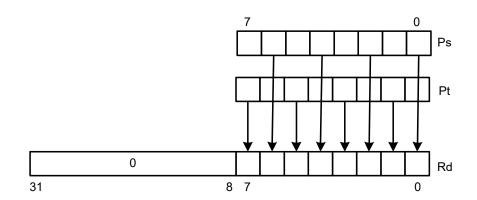

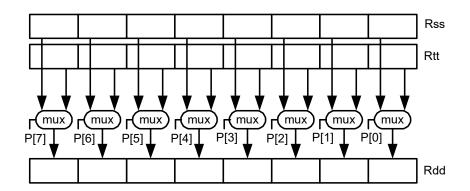

Figure 2-1 Register field symbols

Table 2-2 Register bit field symbols

| Symbol | Meaning                                                                                                   |

|--------|-----------------------------------------------------------------------------------------------------------|

| .sN    | Bits [N-1:0] are treated as a N-bit signed number.                                                        |

|        | For example, R0.s16 means that the least significant 16-bits of R0 are treated as a 16-bit signed number. |

| .uN    | Bits [N-1:0] are treated as a N-bit unsigned number.                                                      |

| .Н     | The most-significant 16 bits of a 32-bit register.                                                        |

| .L     | The least-significant 16 bits of a 32-bit register.                                                       |

#### Examples of *elst* field:

```

EA = Rt.h[1] // .h[1] -> bit field 31:16 in Rt Pd = (Rss.u64 > Rtt.u64) // .u64 -> unsigned 64-bit value Rd = mpyu(Rs.L,Rt.H) // .L/.H -> low/high 16-bit fields

```

The control and predicate registers use the same notation as the general registers, but are written as Cx and Px (respectively) instead of Rx.

## 2.2 General registers

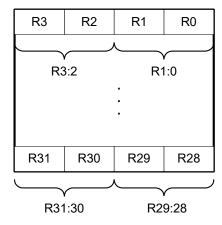

The Hexagon processor has thirty-two 32-bit general-purpose registers (named R0 through R31), which can be accessed either as single registers or as aligned 64-bit register pairs. The general registers contain pointer, scalar, vector, and accumulator data. These registers store operands in virtually all the instructions:

- Memory addresses for load/store instructions

- Data operands for arithmetic/logic instructions

- Vector operands for vector instructions

#### For example:

```

R1 = memh(R0) // Load from address R0

R4 = add(R2,R3) // Add

R28 = vaddh(R11,R10) // Vector add halfword

```

Figure 2-2 General registers

#### Aliased registers

Three of the general registers – R29 through R31 – support subroutines (Section 8.3.2) and the software stack (Chapter 7). The subroutine and stack instructions implicitly modify these registers They have symbol aliases that indicate when these registers are accessed as subroutine and stack registers.

#### For example:

```

SP = add(SP, \#-8) // SP is alias of R29 allocframe // Modifies SP (R29) and FP (R30) call init // Modifies LR (R31)

```

#### Register pairs

The general registers can be specified as register pairs that represent a single 64-bit register. For example:

Table 2-3 General register aliases

| Register | Alias | Name          | Description                                                                                                                                                           |

|----------|-------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R29      | SP    | Stack pointer | Points to the top element of stack in memory.                                                                                                                         |

| R30      | FP    | Frame pointer | Points to the current procedure frame on stack.  Used by external debuggers to examine the stack and determine call sequence, parameters, local variables, and so on. |

| R31      | LR    | Link register | Stores return address of a subroutine call.                                                                                                                           |

NOTE: The first register in a register pair must always be odd-numbered, and the second must be the next lower register.

Table 2-4 General register pairs

| Register | Register pair  |

|----------|----------------|

| R0       | R1:0           |

| R1       |                |

| R2       | R3:2           |

| R3       |                |

| R4       | R5:4           |

| R5       |                |

| R6       | R7:6           |

| R7       |                |

|          |                |

| R24      | R25:24         |

| R25      |                |

| R26      | R27:26         |

| R27      |                |

| R28      | R29:28         |

| R29 (SP) |                |

| R30 (FP) | R31:30 (LR:FP) |

| R31 (LR) |                |

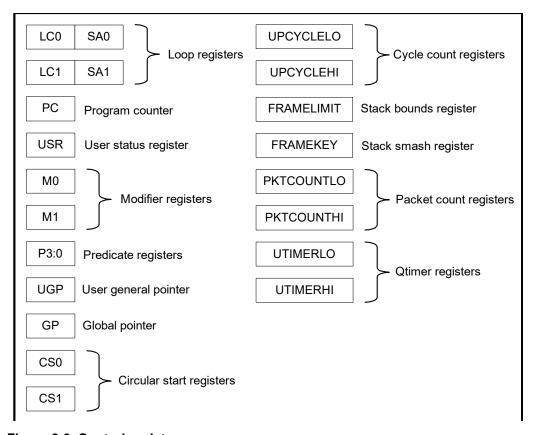

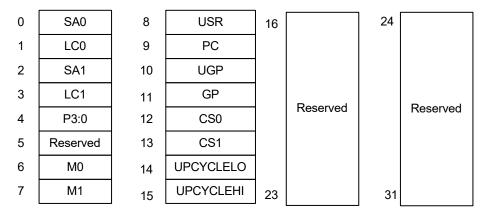

# 2.3 Control registers

The Hexagon processor includes a set of 32-bit control registers that provide access to processor features such as the program counter, hardware loops, and vector predicates.

Unlike general registers, control registers care instruction operands only in the following cases:

- Instructions that require a specific control register as an operand

- Register transfer instructions

#### For example:

NOTE: When a control register is used in a register transfer, the other operand must be a general register.

Figure 2-3 Control registers

### **Aliased registers**

The control registers have numeric aliases (C0 through C31).

Table 2-5 Aliased control registers

| Register   | Alias  | Name                          |

|------------|--------|-------------------------------|

| SA0        | C0     | Loop start address register 0 |

| LC0        | C1     | Loop count register 0         |

| SA1        | C2     | Loop start address register 1 |

| LC1        | C3     | Loop count register 1         |

| P3:0       | C4     | Predicate registers 3:0       |

| reserved   | C5     | _                             |

| MO         | C6     | Modifier register 0           |

| M1         | C7     | Modifier register 1           |

| USR        | C8     | User status register          |

| PC         | C9     | Program counter               |

| UGP        | C10    | User general pointer          |

| GP         | C11    | Global pointer                |

| CS0        | C12    | Circular start register 0     |

| CS1        | C13    | Circular start register 1     |

| UPCYCLELO  | C14    | Cycle count register (low)    |

| UPCYCLEHI  | C15    | Cycle count register (high)   |

| UPCYCLE    | C15:14 | Cycle count register          |

| FRAMELIMIT | C16    | Frame limit register          |

| FRAMEKEY   | C17    | Frame key register            |

| PKTCOUNTLO | C18    | Packet count register (low)   |

| PKTCOUNTHI | C19    | Packet count register (high)  |

| PKTCOUNT   | C19:18 | Packet count register         |

| reserved   | C20-29 | -                             |

| UTIMERLO   | C30    | Qtimer register (low)         |

| UTIMERHI   | C31    | Qtimer register (high)        |

| UTIMER     | C31:30 | Qtimer register               |

NOTE: The control register numbers (0 through 31) specify the control registers in instruction encodings (Chapter 10).

#### Register pairs

The control registers can be specified as register pairs that represent a single 64-bit register. Control registers specified as pairs must use their numeric aliases. For example:

```

C1:0 = R5:4 // C1:0 specifies the LCO/SAO register pair

```

NOTE: The first register in a control register pair must always be odd-numbered, and the second must be the next lower register.

Table 2-6 Control register pairs

| Register | Register pair |

|----------|---------------|

| C0       | C1:0          |

| C1       |               |

| C2       | C3:2          |

| C3       |               |

| C4       | C5:4          |

| C5       |               |

| C6       | C7:6          |

| C7       |               |

|          |               |

| C30      | C31:30        |

| C31      |               |

## 2.3.1 Program counter

The program counter (PC) register points to the next instruction packet to execute. It is modified implicitly by instruction execution, but can be read directly. For example:

```

R7 = PC // Get program counter

```

NOTE: The PC register is read-only: writing to it has no effect.

# 2.3.2 Loop registers

The Hexagon processor includes two sets of loop registers to support nested hardware loops (Section 8.2). Each hardware loop is implemented with a pair of registers containing the loop count and loop start address. The loop registers are modified implicitly by the loop instruction, but are also accessed directly. For example:

```

loop0(start, R4) // Modifies LC0 and SA0 (LC0=R4, SA0=&start) LC1 = R22 // Set loop1 count R9 = SA1 // Get loop1 start address

```

Table 2-7 Loop registers

| Register | Name               | Description                           |

|----------|--------------------|---------------------------------------|

| LCO, LC1 | Loop count         | Number of loop iterations to execute. |

| SAO, SA1 | Loop start address | Address of first instruction in loop. |

### 2.3.3 User status register

The user status register (USR) stores processor status and control bits that are accessible by user programs. The status bits contain the status results of certain instructions, while the control bits contain user-settable processor modes for hardware prefetching. For example:

USR stores the following status and control values:

- Cache prefetch enable (Section 5.10.6)

- Cache prefetch status (Section 5.10.6)

- Floating point modes (Section 4.3.1)

- Floating point status (Section 4.3.1)

- Hardware loop configuration (Section 8.2)

- Sticky saturation overflow (Section 4.2.2)

NOTE: A user control register transfer to USR cannot be grouped in an instruction packet with a floating point instruction (Section 4.3.1).

Whenever a transfer to USR changes the enable trap bits [29:25], an isync instruction (Section 5.11) must execute before the new exception programming can take effect.

Table 2-8 User status register

| RW | Bits | Field    | Description                                                                                                                                                          |

|----|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 32   |          | User status register                                                                                                                                                 |

| R  | 31   | PFA      | L2 prefetch active.                                                                                                                                                  |

|    |      |          | 1: I2fetch instruction in progress     0: I2fetch finished (or inactive)                                                                                             |

|    |      |          | Set when nonblocking l2fetch instruction is prefetching requested data.                                                                                              |

|    |      |          | Remains set until l2fetch prefetch operation completes (or inactive).                                                                                                |

| R  | 30   | reserved | Return 0 if read.                                                                                                                                                    |

|    |      |          | Reserved for future expansion. To remain compatible with future processor versions, software should always write this field with the same value read from the field. |

| RW | 29   | FPINEE   | Enable trap on IEEE inexact.                                                                                                                                         |

| RW | 28   | FPUNFE   | Enable trap on IEEE underflow.                                                                                                                                       |

| RW | 27   | FPOVFE   | Enable trap on IEEE overflow.                                                                                                                                        |

Table 2-8 User status register (cont.)

| RW | Bits  | Field    | Description                                                                                                                                                          |  |

|----|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RW | 26    | FPDBZE   | Enable trap on IEEE divide-by-zero.                                                                                                                                  |  |

| RW | 25    | FPINVE   | Enable trap on IEEE invalid.                                                                                                                                         |  |

| R  | 24    | reserved | Reserved                                                                                                                                                             |  |

| RW | 23:22 | FPRND    | Rounding mode for floating-point instructions.                                                                                                                       |  |

|    |       |          | 00: Round to nearest, ties to even (default) 01: Toward zero 10: Downward (toward negative infinity) 11: Upward (toward positive infinity)                           |  |

| R  | 21:20 | reserved | Return 0 if read.                                                                                                                                                    |  |

|    |       |          | Reserved for future expansion. To remain compatible with future processor versions, software should always write this field with the same value read from the field. |  |

| R  | 19:18 | reserved | Reserved                                                                                                                                                             |  |

| R  | 17    | reserved | Return 0 if read.                                                                                                                                                    |  |

|    |       |          | Reserved for future expansion. To remain compatible with future processor versions, software should always write this field with the same value read from the field. |  |

| RW | 16:15 | HFI      | L1 instruction prefetch.                                                                                                                                             |  |

|    |       |          | 00: Disable 01: Enable (1 line) 10: Enable (2 lines)                                                                                                                 |  |

| RW | 14:13 | HFD      | L1 data cache prefetch.                                                                                                                                              |  |

|    |       |          | Four levels are defined from disabled to aggressive. It is implementation-defined how these levels should be interpreted.  00: disable                               |  |

|    |       |          | 01: conservative<br>10: moderate                                                                                                                                     |  |

|    |       |          | 11: aggressive                                                                                                                                                       |  |

| RW | 12    | PCMME    | Enable packet counting in Monitor mode.                                                                                                                              |  |

| RW | 11    | PCGME    | Enable packet counting in Guest mode.                                                                                                                                |  |

| RW | 10    | PCUME    | Enable packet counting in User mode.                                                                                                                                 |  |

| RW | 9:8   | LPCFGE   | Hardware loop configuration.                                                                                                                                         |  |

|    |       |          | Number of loop iterations (0-3) remaining before pipeline predicate should be set.                                                                                   |  |

| R  | 7:6   | reserved | Return 0 if read.                                                                                                                                                    |  |

|    |       |          | Reserved for future expansion. To remain compatible with future processor versions, software should always write this field with the same value read from the field. |  |

| RW | 5     | FPINPF   | Floating-point IEEE inexact sticky flag.                                                                                                                             |  |

| RW | 4     | FPUNFF   | Floating-point IEEE underflow sticky flag.                                                                                                                           |  |

| RW | 3     | FPOVFF   | Floating-point IEEE overflow sticky flag.                                                                                                                            |  |

| RW | 2     | FPDBZF   | Floating-point IEEE divide-by-zero sticky flag.                                                                                                                      |  |

Table 2-8 User status register (cont.)

| RW | Bits | Field  | Description                                                                                |

|----|------|--------|--------------------------------------------------------------------------------------------|

| RW | 1    | FPINVF | Floating-point IEEE invalid sticky flag.                                                   |

| RW | 0    | OVF    | Sticky saturation overflow.                                                                |

|    |      |        | Saturation occurred     No saturation                                                      |

|    |      |        | Set when saturation occurs while executing instruction that specifies optional saturation. |

|    |      |        | Remains set until explicitly cleared by a USR = Rs instruction.                            |

## 2.3.4 Modifier registers

The following addressing modes use modifier registers (M0 and M1).

#### Indirect autoincrement register addressing

In indirect autoincrement register addressing (Section 5.8.9), the modifier registers store a signed 32-bit value that specifies the increment (or decrement) value. For example:

```

M1 = R0 // Set modifier register R3 = memw(R2++M1) // Load word

```

Table 2-9 Modifier registers used in indirect auto-increment addressing

| Register | Name      | Description                  |

|----------|-----------|------------------------------|

| M0, M1   | Increment | Signed auto-increment value. |

#### Circular addressing

In circular addressing (Section 5.8.10) the modifier registers store the circular buffer length and related "I" values. For example:

Table 2-10 Modifier registers as used in circular addressing

| Name   | RW | Bits  | Field   | Description                        |

|--------|----|-------|---------|------------------------------------|

| M0, M1 |    | 32    |         | Circular buffer specifier.         |

|        | RW | 31:28 | I[10:7] | I value (MSB - see Section 5.8.11) |

|        | RW | 27:24 |         | 0x0                                |

|        | RW | 23:17 | I[6:0]  | I value (LSB)                      |

|        | RW | 16:0  | Length  | Circular buffer length             |

#### Bit-reversed addressing

In bit-reversed addressing (Section 5.8.12) the modifier registers store a signed 32-bit value that specifies the increment (or decrement) value. For example:

Table 2-11 Modifier registers as used in bit-reversed addressing

| Register | Name      | Description                 |

|----------|-----------|-----------------------------|

| M0, M1   | Increment | Signed autoincrement value. |

### 2.3.5 Predicate registers

The predicate registers (P0 through P3) store the status results of the scalar and vector compare instructions (Chapter 6). For example:

```

P1 = cmp.eq(R2, R3) // Scalar compare

if (P1) jump end // Jump to address (conditional)

R8 = P1 // Get compare status (P1 only)

P3:0 = R4 // Set compare status (P0-P3)

```

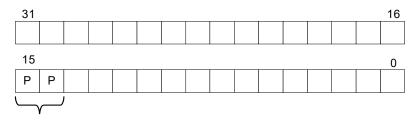

The four predicate registers can be specified as a register quadruple (P3:0), which represents a single 32-bit register.

**Table 2-12 Predicate registers**

| Register       | Bits  | Description             |

|----------------|-------|-------------------------|

| PO, P1, P2, P3 | 8     | Compare status results. |

| P3:0           | 32    | Compare status results. |

|                | 31:24 | P3 register             |

|                | 23:16 | P2 register             |

|                | 15:8  | P1 register             |

|                | 7:0   | P0 register             |

NOTE: Unlike the other control registers, the predicate registers are only eight bits wide because vector compares return a maximum of eight status results.

### 2.3.6 Circular start registers

The circular start registers (CS0 through CS1) store the start address of a circular buffer in circular addressing (Section 5.8.10). For example:

Table 2-13 Circular start registers

| Register | Name           | Description                    |

|----------|----------------|--------------------------------|

| CSO, CS1 | Circular start | Circular buffer start address. |

## 2.3.7 User general pointer register

The user general pointer (UGP) register is a general-purpose control register. For example:

```

R9 = UGP // Get UGP

UGP = R3 // Set UGP

```

NOTE: UGP typically stores the address of thread local storage.

Table 2-14 User general pointer register

| Register | Name                 | Description                       |

|----------|----------------------|-----------------------------------|

| UGP      | User general pointer | General-purpose control register. |

# 2.3.8 Global pointer

The global pointer (GP) is used in GP-relative addressing. For example:

```

GP = R7 // Set GP

R2 = memw(GP+#200) // GP-relative load

```

Table 2-15 Global pointer register

| Name | RW | Bits | Field    | Description                                                                                                                                                                  |

|------|----|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP   |    | 32   |          | Global pointer register                                                                                                                                                      |

|      | RW | 31:6 | GDP      | Global data pointer (Section 5.8.4).                                                                                                                                         |

|      | R  | 5:0  | reserved | Return 0 if read.                                                                                                                                                            |

|      |    |      |          | Reserved for future expansion. To remain forward-compatible with future processor versions, software should always write this field with the same value read from the field. |

### 2.3.9 Cycle count registers

The cycle count registers (UPCYCLELO through UPCYCLEHI) store a 64-bit value containing the number of executed processor cycles since the Hexagon processor was last reset. For example:

```

R5 = UPCYCLEHI // Get cycle count (high)

R4 = UPCYCLELO // Get cycle count (low)

R5:4 = UPCYCLE // Get cycle count

```

NOTE: The RTOS must grant permission to access these registers. Without this permission, reading these registers from user code always returns zero.

Table 2-16 Cycle count registers

| Register  | Name               | Description                          |

|-----------|--------------------|--------------------------------------|

| UPCYCLELO | Cycle count (low)  | Processor cycle count (low 32 bits)  |

| UPCYCLEHI | Cycle count (high) | Processor cycle count (high 32 bits) |

| UPCYCLE   | Cycle count        | Processor cycle count (64 bits)      |

## 2.3.10 Frame limit register

The frame limit register (FRAMELIMIT) stores the low address of the memory area reserved for the software stack (Section 7.3.1). For example:

Table 2-17 Frame limit register

| Register   | Name        | Description                         |

|------------|-------------|-------------------------------------|

| FRAMELIMIT | Frame limit | Low address of software stack area. |

# 2.3.11 Frame key register

The frame key register (FRAMEKEY) stores the key value that XOR-scrambles return addresses when they are stored on the software stack (Section 7.3.2). For example:

```

R2 = FRAMEKEY // Get frame key register

FRAMEKEY = R1 // Set frame key register

```

Table 2-18 Frame key register

| Register | Name      | Description                                                |

|----------|-----------|------------------------------------------------------------|

| FRAMEKEY | Frame key | Key to scramble return addresses stored on software stack. |

### 2.3.12 Packet count registers

The packet count registers (PKTCOUNTLO through PKTCOUNTHI) store a 64-bit value containing the current number of instruction packets executed since a PKTCOUNT register was last written to. For example:

```

R9 = PKTCOUNTHI  // Get packet count (high)

R8 = PKTCOUNTLO  // Get packet count (low)

R9:8 = PKTCOUNT  // Get packet count

```

Packet counting can be configured to operate only in specific sets of processor modes (for example, User mode only, or Guest and Monitor modes only). Bits [12:10] in the user status register control the configuration for each mode (Section 2.3.3).

Packets with exceptions are not counted as committed packets.

NOTE: Each hardware thread has its own set of packet count registers.

The RTOS must grant permission to access these registers. Without this permission, reading these registers from user code always returns zero.

When a value is written to a PKTCOUNT register, the 64-bit packet count value is incremented before the value is stored in the register.

Table 2-19 Packet count registers

| Register   | Name                | Description                           |

|------------|---------------------|---------------------------------------|

| PKTCOUNTLO | Packet count (low)  | Processor packet count (low 32 bits)  |

| PKTCOUNTHI | Packet count (high) | Processor packet count (high 32 bits) |

| PKTCOUNT   | Cycle count         | Processor packet count (64 bits)      |

# 2.3.13 Qtimer registers

The Qtimer registers (UTIMERLO through UTIMERHI) provide access to the Qtimer global reference count value. They enable Hexagon software to read the 64-bit time value without having to perform an expensive AHB load. For example:

```

R5 = UTIMERHI // Get Qtimer reference count (high)

R4 = UTIMERLO // Get Qtimer reference count (low)

R5:4 = UTIMER // Get Qtimer reference count

```

These registers are read-only – they are automatically updated by hardware to always contain the current Qtimer value.

NOTE: The RTOS must grant permission to access these registers. Without this permission, reading these registers from user code always returns zero.

Table 2-20 Qtimer registers

| Register | Name          | Description                                  |

|----------|---------------|----------------------------------------------|

| UTIMERLO | Qtimer (low)  | Qtimer global reference count (low 32 bits)  |

| UTIMERHI | Qtimer (high) | Qtimer global reference count (high 32 bits) |

| UTIMER   | Qtimer        | Qtimer global reference count (64 bits)      |

# 3 Instructions

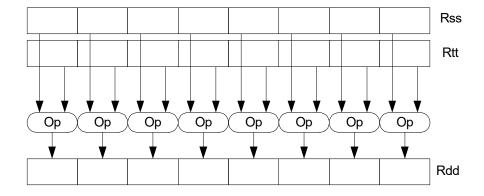

Instructions can be grouped into very long instruction word (VLIW) packets for parallel execution, with each packet containing from one to four instructions. Vector instructions operate on single instruction multiple data (SIMD) vectors.

Instruction encoding is described in Chapter 10.

For detailed descriptions of the Hexagon processor instructions see Chapter 11.

# 3.1 Instruction syntax

Most Hexagon processor instructions have the following syntax:

```

dest = instr_name(source1, source2,...)[:option1][:option2]...

```

The item specified on the left-hand side (LHS) of the equation is assigned the value specified by the right-hand side (RHS). For example:

```

R2 = add(R3,R1) // Add R3 and R1, assign result to R2

```

| Symbol | Meaning                                                                   | Example                     | Min                    | Max                 |

|--------|---------------------------------------------------------------------------|-----------------------------|------------------------|---------------------|

| =      | Assignment of RHS to LHS                                                  | R2 = R3;                    | _                      | _                   |

| ,      | Marks the end of an instruction or group of instructions                  | R2 = R3;                    | -                      | _                   |

| { }    | Instruction packet delimiter; indicates a group of parallel instructions. | {R2 = R3; R5 = R6;}         | _                      | _                   |

| ( )    | Source list delimiter                                                     | R2 = memw(R0 + #100)        |                        |                     |

| 0x     | Indicates hexadecimal number                                              | R2 = #0x1fe;                | _                      | _                   |

| MEMxx  | Access memory. xx specifies the size and type of access.                  | R2 = MEMxx(R3)              | -                      | _                   |

| :rnd   | Perform optional rounding                                                 | R2 = mpy(r1.h,<br>r2.h):rnd | -                      | _                   |

| :<<16  | Shift left by a halfword                                                  | R2 = add(r1.1,r2.1): << 16  | -                      | _                   |

| #      | Immediate constant value                                                  | #100                        | _                      | _                   |

| #uN    | Unsigned N-bit immediate value                                            | R2 = #u16                   | 0                      | 2 <sup>N</sup> -1   |

| #sN    | Signed N-bit immediate value                                              | R2 = add(R3, #s16)          | -2 <sup>N-1</sup>      | 2 <sup>N-1</sup> -1 |

| #mN    | Signed N-bit immediate value                                              | Rd = mpyi(Rs, #m9)          | -(2 <sup>N-1</sup> -1) | 2 <sup>N-1</sup> -1 |

| Symbol            | Meaning                                                                                             | Example                                          | Min                                   | Max                                    |

|-------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------|----------------------------------------|

| #uN:S             | Unsigned N-bit immediate value representing integral multiples of 2 <sup>S</sup> in specified range | R2 = memh(#u16:1)                                | 0                                     | $(2^{N}-1)\times 2^{S}$                |

| #sN:S             | Signed N-bit immediate value representing integral multiples of 2 <sup>S</sup> in specified range   | Rd = memw(Rs++#s4:2)                             | (-2 <sup>N-1</sup> ) × 2 <sup>S</sup> | (2 <sup>N-1</sup> -1) × 2 <sup>S</sup> |

| #rN:S             | Same as #sN:S, but value is offset from PC of current packet                                        | call #r22:2                                      | $(-2^{N-1}) \times 2^S$               | (2 <sup>N-1</sup> -1) × 2 <sup>S</sup> |

| ##                | 32-bit immediate constant value. Same as #, but associated value (u, s, m, r) is 32 bits            | ##2147483647                                     | -                                     | _                                      |

| usat <sub>N</sub> | Saturate value to unsigned N-bit number                                                             | usat <sub>16</sub> (Rs)                          | 0                                     | 2 <sup>N</sup> -1                      |

| sat <sub>N</sub>  | Saturate value to signed N-bit number                                                               | sat <sub>16</sub> (Rs)                           | -2 <sup>N-1</sup>                     | 2 <sup>N-1</sup> -1                    |

| sxt x->y          | Sign-extend value from x to y bits                                                                  | sxt32->64(Rs)                                    | _                                     | _                                      |

| zxt x->y          | Zero-extend value from x to y bits                                                                  | zxt32->64(Rs)                                    | _                                     | _                                      |

| >>>               | Logical right shift                                                                                 | Rss >>> offset                                   | _                                     | _                                      |

| :endloopX         | Loop end  X specifies loop instruction (0 or 1)                                                     | :endloop0                                        |                                       |                                        |

| :t                | Direction hint (jump taken)                                                                         | <pre>if (P0.new) jump:t target</pre>             |                                       |                                        |

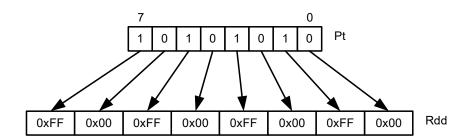

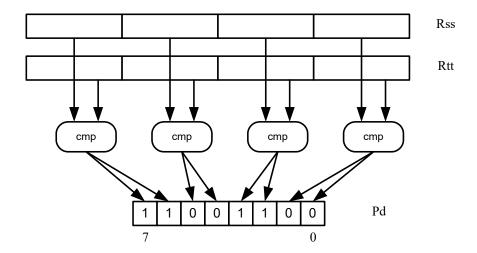

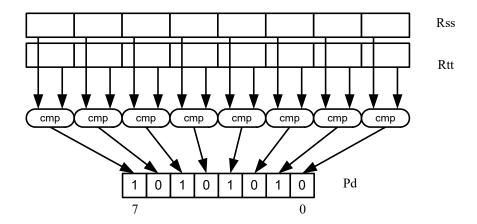

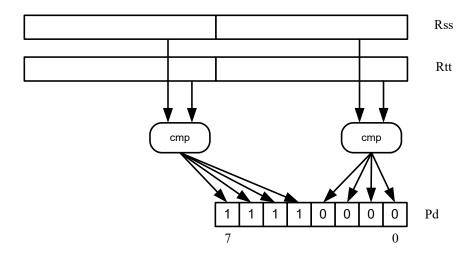

| :nt               | Direction hint (jump not taken)                                                                     | <pre>if (!P1.new) jump:nt target</pre>           |                                       |                                        |