Qualcomm Technologies International, Ltd.

## **QCC711 Bluetooth Low Energy**

Production Information Data Sheet 80-WL711-1 Rev. AH March 14, 2025

#### **Device description**

- Low-power Single Mode Bluetooth® Low Energy SoC

- Bluetooth v5.4 specification

- Tri-core processor architecture including a dedicated processor for customer applications

- High security capabilities and services enabled by a true Root-of-Trust processor

#### **Applications**

- Electronic shelf label (ESL) a

- Beacons

- Smart devices and accessories

- Smart home

- Building automation

- Wide range of Bluetooth Low Energy IoT

- a ESL is restricted to licensed OEMs

#### **Features**

- Qualified to Bluetooth v5.4 specification

- Arm Cortex-M3 (32 MHz)

Application Processor

- Arm Cortex-M0 (32 MHz)

Bluetooth Processor

- 26 PIC

- Peripheral interfaces include: I<sup>2</sup>C, SPI, UART

- Flexible counter timer

- Quad SPI flash memory controller

- Analog I/O, battery voltage monitor, integrated temperature sensor

- Hosted and hostless modes

- Integrated PMU: 1.71 V to 3.6 V SMPS and LDOs

- 48-lead 5.6 mm x 5.6 mm x

0.85 mm, 0.4 mm pitch QFN

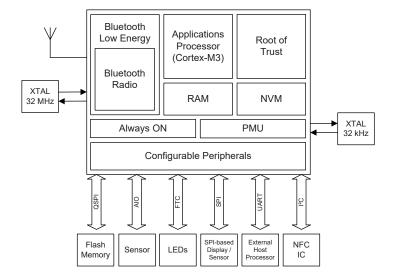

#### System architecture

## QCC711 description

QCC711 is a low-power wireless single mode Bluetooth Low Energy SoC targeted at:

- Beacon applications for asset tracking and monitoring

- Smart devices and accessories for heath/fitness, remote control, computer peripherals

- Bluetooth on-boarding for Wi-Fi access points

- Smart homes for switches and sensors

- Building automation for monitoring and control

- A wide range of Bluetooth Low Energy IoT applications

#### **Processors**

QCC711 has dedicated processors with shared on-chip memory, SRAM and NVM, for Applications, Bluetooth Low Energy, and Root of Trust subsystems. The Applications subsystem uses an Arm Cortex-M3 processor for OEM application code. Code can run with or without an RTOS providing product designers with product customization flexibility.

#### **Bluetooth**

A dedicated Arm Cortex-M0 processor for the QCC711 Bluetooth subsystem executes the Bluetooth Low Energy stack in ROM, enabling consistent execution without processor resource competition. QCC711 supports Bluetooth v5.4 specification, single-mode Bluetooth Low Energy.

#### I/O (PIO)

QCC711 has a wide range of I/O and peripheral options available, including, QSPI, SPI, UART, I<sup>2</sup>C, FTC, and analog measurement. By employing these peripherals in various combinations, a wide range of applications are achievable.

#### Software development tools

QCC711 is driven by a flexible software platform. For information on QCC711 development tools, Bluetooth, and other supported features, see CreatePoint.

#### **QCC711 operating modes**

QCC711 operates in one of two modes:

- **Hostless mode**: QCC711 is supplied directly from a battery, or an external regulator, and clocked from dedicated crystals. A sleep crystal offers lower system power to enable a longer battery life.

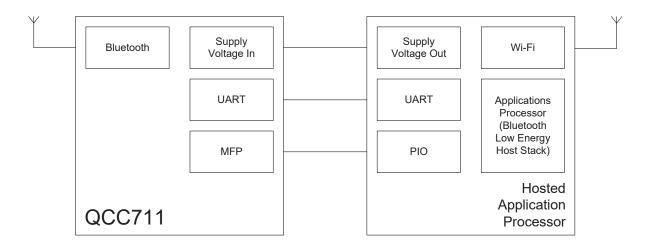

- Hosted mode: QCC711 connects to another hosted device using HCI over UART. For example, as shown in the

following figure, an application processor device (access point). In this example, the Bluetooth Low Energy host

stack is located in the application processor, which provides the voltage supply and uses the MFP for on/off

control.

QCC711 connected in hosted mode

**RELATED INFORMATION**

"QCC711 example application schematic" on page 49

# Ordering information

| Device |                          | Order number                                 |                 |                                                                                |

|--------|--------------------------|----------------------------------------------|-----------------|--------------------------------------------------------------------------------|

| Device | Type                     | Size                                         | Shipment method | Order Humber                                                                   |

| QCC711 | QFN 48-lead<br>(Pb free) | 5.6 mm x 5.6 mm x<br>0.85 mm 0.4 mm<br>pitch | Tape and reel   | QCC-711-1-MQFN48C-TR-02-1<br>(v2.0) and<br>QCC-711-1-MQFN48C-TR-03-1<br>(v2.1) |

#### NOTE

Your attention is drawn to QTIL's Terms of Supply, see <a href="http://www.qualcomm.com/salesterms">http://www.qualcomm.com/salesterms</a> or please request a copy), in particular the section covering Product Warranties and Disclaimers. Please note that the product warranty differs for production, pre-production, and other versions.

Production status minimum order quantity is 4 kpcs.

**Supply chain:** QTIL's manufacturing policy is to multisource volume products. For further details, contact your local sales account manager or representative.

## **QTIL** contacts

General information http://www.qualcomm.com

Sales information qcsales@qti.qualcomm.com

Compliance and standards product.compliance@qti.qualcomm.com

# QCC711 device details

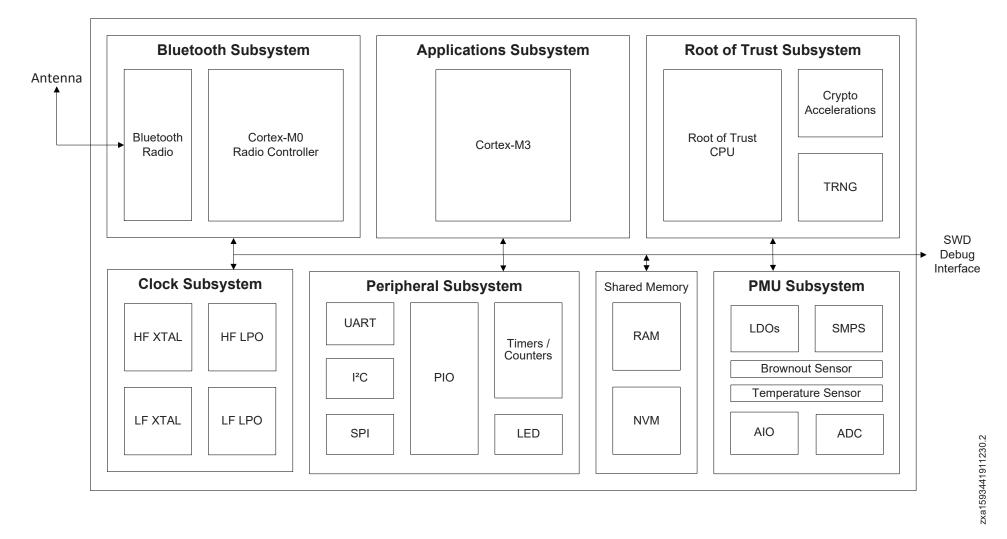

#### Bluetooth subsystem

- Arm Cortex-M0 (32 MHz) processor

- Qualified to Bluetooth v5.4 specification

- Single mode Bluetooth Low Energy

- Bluetooth Low Energy, advertising extensions, periodic advertising

- □ 1 Mbps and 2 Mbps support

- Single ended antenna connection with on-chip balun and Tx/Rx switch

- □ Tx power up to 7 dBm

- Rx sensitivity -96 dBm

- -99 dBm (boost) at 1 Mbps

- Bluetooth Low Energy Class 1 support

#### Application subsystem

- Arm Cortex-M3 (32 MHz) processor running OEM application code

- Timers/counters include 1 x 44-bit timer, 1 x 32-bit timer, low energy timer, and watchdog timer

#### Root-of-Trust subsystem

- RISC-V (32 MHz) processor

- QCC711 security feature controller, with hardware accelerators for AES, SHA, PKA, and PRNG

#### **Shared access-controlled memory**

- SRAM 64 KB for customer application

- NVM 384 KB for customer application

#### Clocks

- 32 MHz crystal (external)

- HFLPO (internal)

- 32 kHz crystal (external)

- LFLPO (internal)

#### Radio current consumption at 3 V

- Tx current consumption:

- 9.9 mA at 0 dBm

- 16.9 mA at 7 dBm

- Rx current consumption:

- 4.6 mA at -98 dBm

- Sleeping power consumption between radio events (with 32 KB RAM retention and MCUs in Sleep state):

- □ <2 µA

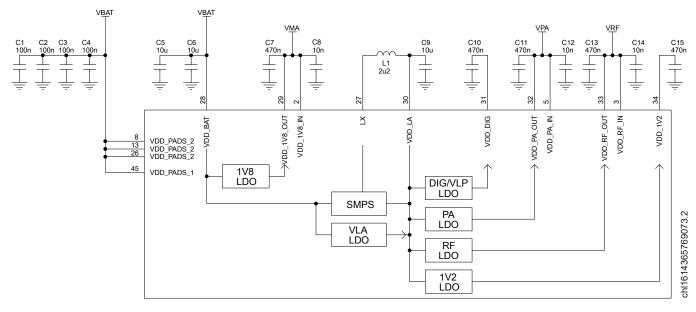

#### Power management

- Integrated power management unit (PMU)

- QCC711 runs directly from a 3 V coin-cell battery, supports (1.71 V to 3.6 V)

- Single switch-mode power supply (SMPS) and LDOs

- Battery brownout sensor

- Asynchronous wake events are not supported for example from a PIO<sup>a</sup>

- Wake up from Sleep state using an interrupt on a PIO is not supported<sup>a</sup>

<sup>&</sup>lt;sup>a</sup> Applies to (v2.0) only. For more details, see QCC711 Bluetooth Low Energy Device Revision Guide (80-WL711-4)

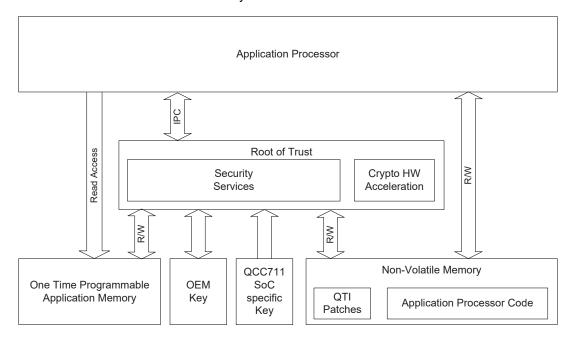

#### Security

- Root-of-Trust subsystem dedicated CPU provides secure execution environment

- Security capabilities:

- General-purpose public key accelerator (PKA) with support:

- NIST curves P-256, P-521

- ECC Private/Public Key generation, ECDH, ECDSA

- General-purpose symmetric crypto accelerator support:

- AES128/256

- SHA2-256/512

- Crypto Block Cipher Modes (CBC, GCM, CTR)

- MAC modes: HMAC-SHA2-256

- Key Derivation Functionality (HKDF, RFC5869)

- TRNG

- Security services:

- Secure boot

- Secure debug

- Remote attestation

- Secure provisioning

- Secure communication and OTA-Firmware update

#### **Debug and tools**

- SWD and Segger debug support.

- IAR Embedded Workbench for Arm

#### Qualcomm Technologies Inc. (QTI) signature enabled, Root-of-Trust managed, system on-chip (SoC) specific keying material

- SoC specific keying material enables:

- Device authentication: useful in distinguishing an authentic SoC device from one that is not (an unauthorized clone)

- Remote attestation: enables an original equipment manufacturer (OEM) or service provider to determine the security state of the SoC at any given time

- Onboarding: the process of delivering configuration data to a specific application device in the field

- SoC specific keying material as part of the QCC711 Rootof-Trust solution, is designed to create on demand:

- a signed token encapsulating optional attestation statements

- attestation and encryption public keys

- a QTI signature: supplied at the time of SoC manufacturing

Not all interfaces are available concurrently; some combinations are excluded.

#### Peripherals and physical interfaces<sup>a</sup>

- 2 x SPI for SPI-based display/sensor (3-wire or 4-wire mode)

- 1 x SPI controller for external SPI flash memory (4 wire, or quad-mode 6 wire)

- 4 x FTC channels

- 4 x LED driver, combining FTC channels

- 3 x UART for Application subsystem (2 x 9-bit and 1 x

- 2 x I<sup>2</sup>C controller-only interfaces for EEPROM and/or NFC. or other I2C peripherals

- 1 x I<sup>2</sup>C peripheral-only interface

- 26 x PIO, 4 of which have analog capability

- 2 x AIO inputs for ambient light sensor

- 1 x ADC (10-bit, 0 V to 3.6 V range or 0 V to 1.8 V range)

- 2 x Voltage comparators; to separately monitor battery voltage level during application processor activity or radio Tx operation

- 1 x MFP input-only; software configurable

- Internal temperature sensor

#### Package and compliance

- 48-lead 5.6 mm x 5.6 mm x 0.85 mm, 0.4 mm pitch QFN

- Temperature range -40 to 85 °C

- Green (restriction of hazardous substances (RoHS) compliant, and no antimony or halogenated flame retardants)

# QCC711 functional block diagram

## QCC711 functional block diagram

# **Revision history**

| Revision | Date           | Change reason                                                                                                                                                                                                                                                    |  |  |  |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AA       | December 2021  | Updated with v2.0 silicon updates to Document title, Front page, Ordering information, Device details, and Sections 1.1, 2.2, 3.8, 6, 7, 8.4.3, 8.4.4, 9.1, 9.2, 11.4, 11.7, 12, 13.1, 13.5, 13.6, 14.1, 14.2, 15.1, 15.2, 15.3, 18.3.2, 19, 19.1, and Glossary. |  |  |  |

| AB       | October 2022   | Updates to Front page, Description, Ordering information, Device details, and Sections 1 1.2, 1.5, 1.6, 2, 2.1, 4.3, 8.4, 8.4.2, 9.1, 9.2, 11, 12, 14, 14.1, 14.2, 15, 15.1, 15.2, 15.3, 1 19.1, 19.2, and Document references, and Glossary.                    |  |  |  |

| AC       | December 2022  | Update to Section 19.1.                                                                                                                                                                                                                                          |  |  |  |

| AD       | July 2023      | Updated to QCC711 throughout. Updates to Front page, Description, Ordering information, Device details, and Sections 1.1, 2, 8.1, 13.2, 15, 15.1, 15.3, 19, 19.1, 19.2, and Document references, and Glossary.                                                   |  |  |  |

| AE       | August 2023    | Updated to Production Information status (v2.0).                                                                                                                                                                                                                 |  |  |  |

| AF       | September 2023 | Updated to Production Information status (v2.1).                                                                                                                                                                                                                 |  |  |  |

| AG       | January 2024   | Minor editorial updates.                                                                                                                                                                                                                                         |  |  |  |

| AH       | March 2025     | Editorial updates.                                                                                                                                                                                                                                               |  |  |  |

## Status information

QTIL Product Data Sheets progress according to the following formats: Advance Information, Engineering Sample, Pre-production Information, and Production Information. The status of this document is **Production Information**.

#### **Advance Information**

Information for designers concerning QTIL product in development. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

#### **Engineering Sample**

Information about initial devices. Devices are untested or partially tested prototypes, their status is described in an Engineering Sample Release Note. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All detailed specifications including pinouts and electrical specifications may be changed by QTIL without notice.

#### **Pre-production Information**

Pinout and mechanical dimension specifications finalized. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All electrical specifications may be changed by QTIL without notice.

#### **Production Information**

Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

Production Data Sheets supersede all previous document versions.

## **Device implementation**

As the feature-set of the QCC711 is firmware build-specific, see the relevant software release note for the exact implementation of features on the QCC711.

## Life support policy and use in safety-critical applications

QTIL products are not authorized for use in life-support or safety-critical applications. Use in such applications is done at the sole discretion of the customer. QTIL will not warrant the use of its devices in such applications.

# Contents

| QCC711 description                                          | 2          |

|-------------------------------------------------------------|------------|

| Ordering information                                        | 4          |

| QTIL contacts                                               | 4          |

| QCC711 device details                                       | 5          |

| QCC711 functional block diagram                             | 7          |

| Revision history                                            | 8          |

| Status information                                          | 9          |

| Device implementation                                       | 9          |

| Life support policy and use in safety-critical applications | 9          |

| 1 Package information                                       | ١5         |

| 1.1 Chip marking                                            | 5۔         |

| 1.2 QCC711 package dimensions diagram                       | 6۔         |

| 1.3 QCC711 lead allocations                                 | ر          |

| 1.4 QCC711 device terminal functions                        | 8.         |

| 1.4.1 Radio device terminal functions                       | 8.         |

| 1.4.2 Clock device terminal functions                       | .8         |

| 1.4.3 PIO device terminal functions                         | 9          |

| 1.4.4 Control device terminal functions                     | 20         |

| 1.4.5 Power supply device terminal functions                | <u>'</u> 1 |

| 1.4.6 Ground device terminal functions                      | <u>'</u> 1 |

| 1.5 QCC711 PCB design and assembly considerations           | 12         |

| 1.5.1 Typical solder reflow profile                         | <u>2</u>   |

| 1.6 Moisture sensitivity level                              | 2          |

| 2 Bluetooth subsystem                                       | !3         |

| 2.1 Bluetooth v5.4                                          | 23         |

| 2.2 Bluetooth radio                                         | 23         |

| 3 Crystal oscillator                                        | <u>'</u> 4 |

| 3.1 LPO CAL                                                 | <u>2</u> 4 |

| 3.2 32.768 kHz crystal                                      | 25         |

| 3.3 32 MHz crystal                                          | 25         |

| 3.4 Global clock controller                                 | 26         |

| 3.4.1 Timers                                                | 26         |

| 3.5 32.768 kHz crystal performance specification            | <u>2</u> 6 |

| 3.6 32.768 kHz crystal selection considerations             | 27         |

| 3.7 32 MHz crystal performance specification       | . 27 |

|----------------------------------------------------|------|

| 3.8 32 MHz crystal selection considerations        | . 27 |

| 4 System power states                              | . 28 |

| 4.1 Off state                                      | . 28 |

| 4.2 Active state                                   | . 28 |

| 4.3 Sleep state                                    | . 28 |

| 4.4 Hibernate state                                | . 29 |

| 5 Applications subsystem                           | . 30 |

| 5.1 Application subsystem features                 | . 30 |

| 6 SRAM module                                      | . 31 |

| 7 NVM module                                       | . 32 |

| 8 Peripheral module                                | . 33 |

| 8.1 Peripheral module features                     | . 34 |

| 8.2 QSPI controller                                | . 35 |

| 8.3 Flexible timer/counter                         | . 35 |

| 8.4 QCC711 serial engines and supported interfaces | . 37 |

| 8.4.1 UART                                         | 37   |

| 8.4.2 I <sup>2</sup> C interfaces                  | . 38 |

| 8.4.3 3-wire SPI for display                       | . 39 |

| 8.4.4 4-wire SPI for display                       | . 39 |

| 8.4.5 True 4-wire SPI                              | . 39 |

| 9 PIO                                              | . 40 |

| 9.1 QCC711 PIO multiplexing functions              | . 40 |

| 9.2 Multi-function pin                             | . 43 |

| 10 Root-of-Trust subsystem                         | . 44 |

| 10.1 Security services                             | 44   |

| 10.2 Security capabilities                         | . 45 |

| 11 PMU subsystem                                   | . 46 |

| 11.1 PMU subsystem features                        | . 46 |

| 11.2 10-bit SAR ADC                                | . 47 |

| 11.3 Battery voltage sensor                        | 47   |

| 11.4 Battery load cells                            | . 47 |

| 11.5 Analog inputs on PIO                          | . 47 |

| 11.6 Reading an LDR using a PIO                    | . 48 |

| 11.7 PMU temperature sensor measurement accuracy   | 48   |

| 12 QCC711 example application schematic            | 49   |

| 13 Electrical characteristics                      | . 50 |

| 13.1 Absolute maximum ratings                      | 50   |

| 13.2 Recommended operating conditions                   | . 51 |

|---------------------------------------------------------|------|

| 13.3 SMPS                                               | . 52 |

| 13.4 Digital terminals                                  | 52   |

| 13.5 MFP terminals                                      | . 52 |

| 13.6 Analog terminals                                   | . 53 |

| 14 Bluetooth performance                                | 54   |

| 14.1 Bluetooth radio characteristics: Low Energy 1 Mb/s | 54   |

| 14.2 Bluetooth radio characteristics: Low Energy 2 Mb/s | 55   |

| 15 Power consumption                                    | 56   |

| 15.1 Transmitter power consumption                      | 56   |

| 15.2 Receiver power consumption                         | . 56 |

| 15.3 Sleep and Hibernate state power consumption        | 56   |

| 16 RoHS compliance                                      | . 57 |

| 17 Software development and tools                       | 58   |

| 18 Carrier, storage, and handling information           | . 59 |

| 18.1 Carrier                                            | . 59 |

| 18.1.1 Tape and reel information                        | . 59 |

| 18.2 Storage                                            | 60   |

| 18.2.1 Bagged storage conditions                        | 60   |

| 18.2.2 Out-of-bag duration                              | . 60 |

| 18.3 Handling                                           | . 60 |

| 18.3.1 Baking                                           | . 60 |

| 18.3.2 Electrostatic discharge                          | . 61 |

| 18.4 Bar code label and packing for shipment            | 61   |

| 19 Part reliability                                     | . 62 |

| 19.1 Silicon reliability results                        | . 62 |

| 19.2 Package reliability results                        | 63   |

| Document references                                     | . 64 |

| Classami                                                | 6E   |

# **Tables**

| Table 1-1: QCC711 chip marking content                                  | 15 |

|-------------------------------------------------------------------------|----|

| Table 1-2: Pad type definitions for device terminal functions           | 18 |

| Table 1-3: QCC711 Radio device terminal functions                       | 18 |

| Table 1-4: QCC711 Clock device terminal functions                       | 18 |

| Table 1-5: QCC711 PIO power supply and reset definitions                | 19 |

| Table 1-6: QCC711 PIO device terminal functions                         | 20 |

| Table 1-7: QCC711 control device terminal functions                     | 20 |

| Table 1-8: QCC711 Power supply device terminal functions                | 21 |

| Table 1-9: QCC711 Ground device terminal functions                      | 21 |

| Table 3-1: QCC711 32.768 kHz crystal specification                      | 26 |

| Table 3-2: Electrical requirements                                      | 27 |

| Table 8-1: QCC711 peripheral IPs                                        | 34 |

| Table 8-2: QCC711 serial engines and supported interfaces               | 37 |

| Table 8-3: Default port mappings for QCC711 serial engines              | 37 |

| Table 8-4: UART configuration options                                   | 38 |

| Table 8-5: Supported UART baud rates                                    | 38 |

| Table 9-1: QCC711 PIO multiplexing functions                            | 40 |

| Table 14-1: Bluetooth Low Energy 1 Mb/s transmitter performance at 25°C | 54 |

| Table 14-2: Bluetooth Low Energy 1 Mb/s receiver performance at 25°C    | 54 |

| Table 14-3: Bluetooth Low Energy 2 Mb/s transmitter performance at 25°C | 55 |

| Table 14-4: Bluetooth Low Energy 2 Mb/s receiver performance at 25°C    | 55 |

| Table 15-1: Transmitter power consumption                               | 56 |

| Table 15-2: Receiver power consumption                                  | 56 |

| Table 15-3: Sleep and Hibernate state power consumption                 | 56 |

| Table 18-1: QCC711 carrier tape dimensions                              | 59 |

| Table 19-1: Silicon reliability results                                 | 62 |

| Table 19-2: Package reliability results                                 | 63 |

# **Figures**

| QCC711 functional block diagram                                      | 7  |

|----------------------------------------------------------------------|----|

| Figure 1-1: QCC711 chip marking                                      | 15 |

| Figure 1-2: QCC711 package dimensions diagram                        | 16 |

| Figure 1-3: QCC711 lead allocations (orientation from top of device) | 17 |

| Figure 3-1: Crystal oscillator                                       | 24 |

| Figure 4-1: QCC711 power states diagram                              | 28 |

| Figure 8-1: QCC711 Peripheral module                                 | 33 |

| Figure 10-1: QCC711 Root-of-Trust subsystem                          | 44 |

| Figure 11-1: PMU subsystem                                           | 46 |

| Figure 11-2: Battery resistance                                      | 47 |

| Figure 12-1: QCC711 example application schematic                    | 49 |

| Figure 18-1: QCC711 carrier tape and part orientation                | 59 |

| Figure 18-2: Tape handling recommendations                           | 60 |

# vwm1593441902980.1

# 1 Package information

QCC711 is available in a 5.6 mm x 5.6 mm x 0.85 mm 48-lead QFN package.

## 1.1 Chip marking

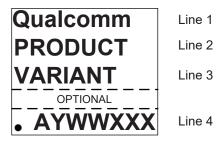

Chip marking identifies lot-specific information about QCC711.

Figure 1-1 shows the product marking for QCC-711-1-MQFN48C-TR-02-1 (v2.0) and QCC-711-1-MQFN48C-TR-03-1 (v2.1) in a 48-lead 5.6 mm x 5.6 mm x 0.85 mm QFN package.

Figure 1-1 QCC711 chip marking

**NOTE** Figure 1-1 is not to scale. The marking font and image are for illustration purposes only.

The circle location mark identifies lead 1.

Table 1-1 QCC711 chip marking content

| Line     | Description                                                  | Definition                                                                  |  |  |

|----------|--------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| 1        | Qualcomm text                                                | -                                                                           |  |  |

| 2        | Product name                                                 | QCC711                                                                      |  |  |

| 3        | Config, revision, and feature codes                          | 102 (v.2.0) 103 (v2.1)                                                      |  |  |

| OPTIONAL | Space for optional trace information; can be 1 or more lines | -                                                                           |  |  |

| 4        | Manufacturing trace code                                     | AYWWXXX  A: Assembly site code Y: Year WW: Work week XXX: Lot serial number |  |  |

# ajr1581942861912.4

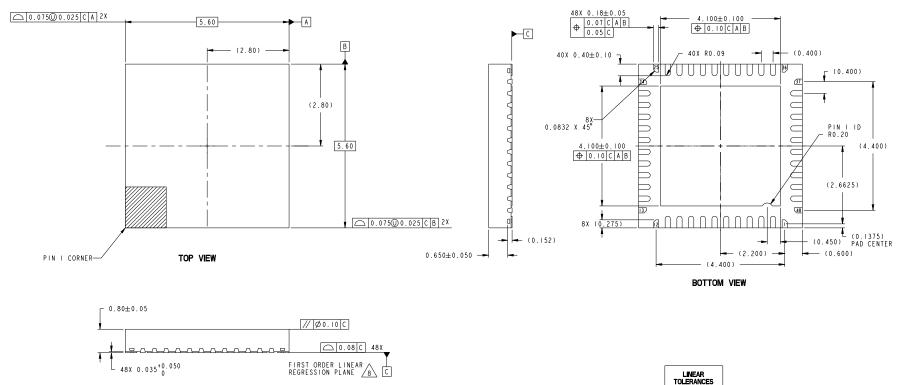

## QCC711 package dimensions diagram

Figure 1-2 shows the dimensions of the QCC711 package from top, bottom, and side views.

- CHANGE APPROVAL, ALL CHANGES SHALL BE IN ACCORDANCE WITH 80-V3652-I GENERAL SUPPLIER QUALITY REQUIREMENTS.

- QUALCOMM SUPPLIED ELECTRONIC DATABASE(S) ARE FOR REFERENCE ONLY. DIMENSIONAL INFORMATION ON CURRENT REVISION OF RELEASED DRAWING TAKES PRECEDENCE OVER ELECTRONIC DATABASE(S).

- WORKMANSHIP SHALL BE IN ACCORDANCE WITH QUALCOMM PACKAGE ASSEMBLY WORKMANSHIP STANDARD 80-V0691-2

- INTERPRET DIMENSIONS AND TOLERANCES PER ASME YI4.5-2009.

- 2. ALL DIMENSIONS SHOWN ON THIS DRAWING ARE IN MILLIMETERS (MM).

- I. INTERPRET DRAWING PER ASME YI4.100

NOTES: UNLESS OTHERWISE SPECIFIED.

PRIMARY DATUM ——— IS DETERMINED BY THE FIRST ORDER LMS REGRESSION PLANE PASSING THROUGH THE CENTERS OF EACH PAD.

7. THE SURFACE FINISH OF THE PACKAGE SHALL BE EDM CHARMILLE #24-#27.

X.XX ±0.10 X.XXX ±0.050 METRIC ONLY THIRD ANGLE PROJECTION UNLESS OTHERWISE SPECIFIED

DIMENSION UNITS ARE AS NOTED/PER NOTE 2

AND APPLY AFTER SURFACE TREATMENT

X ±1 X.X ±0.3

Figure 1-2 QCC711 package dimensions diagram

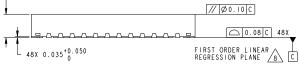

## 1.3 QCC711 lead allocations

QCC711 has a 48-lead QFN package. Lead 25 (VSS) and the ground paddle are used for electrical grounding, mechanical strength, and thermal continuity. Figure 1-3 shows QCC711 lead allocations.

Figure 1-3 QCC711 lead allocations (orientation from top of device)

## 1.4 QCC711 device terminal functions

The leads on the QCC711 are grouped into various terminal functions. The device terminal functions include:

- Radio

- Clock

- PIO

- Control

- Power supplies

- Ground

Table 1-2 lists pad type definitions for the device terminal functions.

Table 1-2 Pad type definitions for device terminal functions

| Symbol | Description            | Symbol                                                                                      | Description                      |  |  |

|--------|------------------------|---------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Al     | Analog input           | Р                                                                                           | Voltage supply                   |  |  |

| AO     | Analog output          | Z                                                                                           | High-impedance (high-Z) output   |  |  |

| AIO    | Analog input or output | OD                                                                                          | Open Drain                       |  |  |

| DIO    | Bidirectional digital  | Pad pull deta                                                                               | Pad pull details for digital I/O |  |  |

| DI     | Digital input          | PU Input signals with weak internal pull-up, to prevent signal from floating when left open |                                  |  |  |

| DO     | Digital output         | PD Input signals with weak internal pull-down, to preve from floating when left open        |                                  |  |  |

| GND    | Ground                 | NP                                                                                          | Contains no internal pull        |  |  |

| NC     | No connection          |                                                                                             |                                  |  |  |

#### 1.4.1 Radio device terminal functions

Table 1-3 QCC711 Radio device terminal functions

| Signal name | Lead<br>number | Pad type | Power domain | Description                 |  |

|-------------|----------------|----------|--------------|-----------------------------|--|

| RF_ANT      | 4              | RF       | -            | Bluetooth transmit/receive. |  |

#### 1.4.2 Clock device terminal functions

Table 1-4 QCC711 Clock device terminal functions

| Signal name | Lead<br>number | Pad type | Power domain Description |                                   |

|-------------|----------------|----------|--------------------------|-----------------------------------|

| XTAL32K_IN  | 37             | Al       | -                        | XTAL input for 32.768 kHz clock.  |

| XTAL32K_OUT | 36             | AO       | -                        | XTAL output for 32.768 kHz clock. |

| XTAL32M_IN  | 48             | Al       | -                        | XTAL input for 32 MHz clock.      |

| XTAL32M_OUT | 1              | AO       | -                        | XTAL output for 32 MHz clock.     |

#### 1.4.3 PIO device terminal functions

PIOs have different states according to the power or reset state of the device.

#### QCC711 reset states

- **POR\_RST\_A**: a power on reset (POR) from the on-chip power management unit (PMU) in hostless mode. The POR sequence is triggered in response to a battery attach event **before** the core supply is stable.

- **POR\_RST\_B**: a POR from the on-chip PMU in hostless mode. The POR sequence is triggered in response to a battery attach event **after** the core supply is stable.

- COLD\_RST: similar to a POR. A cold reset causes a full power OFF/ON sequence, and can be triggered by:

- software requests

- a watchdog bite event (in mission mode)

- a brownout event

- □ a multi-function pin (MFP) input >10 s

- **WARM\_RST**: this reset is triggered **before** the chip enters Low Power mode.

Table 1-5 QCC711 PIO power supply and reset definitions

| PIO port   | Power domain | POR_RST_A | POR_RST_B      | COLD_RST       | WARM_RST             |

|------------|--------------|-----------|----------------|----------------|----------------------|

| PIO[25:11] | VDD_PADS_2   | Hi-Z      | Weak pull down | Weak pull down | Latched <sup>a</sup> |

| PIO[10]    | VDD_PADS_2   | Hi-Z      | SWD_DIO        | SWD_DIO        | Latched <sup>a</sup> |

| PIO[9]     | VDD_PADS_2   | Hi-Z      | SWD_CLK        | SWD_CLK        | Latched <sup>a</sup> |

| PIO[8:0]   | VDD_PADS_1   | Hi-Z      | Weak pull down | Weak pull down | Latched <sup>a</sup> |

<sup>&</sup>lt;sup>a</sup> In WARM\_RST state, all PADs are latched to the state before QCC711 enters Low Power mode.

**NOTE** QCC711 PIOs have extensive multiplexing capabilities to access numerous digital peripherals. For details, see *Related Information*.

Table 1-6 QCC711 PIO device terminal functions

| Signal name | Lead<br>number | Pad type | Power domain           | Description                             |  |

|-------------|----------------|----------|------------------------|-----------------------------------------|--|

| PIO[25]     | 24             | DIO / AI | VDD_PADS_2             | Generic PIO, Analog inputs configurable |  |

| PIO[24]     | 23             | DIO / AI | VDD_PADS_2             | Generic PIO, Analog inputs configurable |  |

| PIO[23]     | 22             | DIO / AI | VDD_PADS_2             | Generic PIO, Analog inputs configurable |  |

| PIO[22]     | 21             | DIO / AI | VDD_PADS_2             | Generic PIO, Analog inputs configurable |  |

| PIO[21]     | 20             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[20]     | 19             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[19]     | 18             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[18]     | 17             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[17]     | 16             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[16]     | 15             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[15]     | 14             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[14]     | 12             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[13]     | 11             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[12]     | 10             | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[11]     | 9              | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[10]     | 7              | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[9]      | 6              | DIO      | VDD_PADS_2             | Generic PIO                             |  |

| PIO[8]      | 47             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

| PIO[7]      | 46             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

| PIO[6]      | 44             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

| PIO[5]      | 43             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

| PIO[4]      | 42             | DIO      | VDD_PADS_1 Generic PIO |                                         |  |

| PIO[3]      | 41             | DIO      | VDD_PADS_1 Generic PIO |                                         |  |

| PIO[2]      | 40             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

| PIO[1]      | 39             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

| PIO[0]      | 38             | DIO      | VDD_PADS_1             | Generic PIO                             |  |

**RELATED INFORMATION**

"PIO" on page 40

## 1.4.4 Control device terminal functions

Table 1-7 QCC711 control device terminal functions

| Signal name | Lead<br>number | Pad type | Power domain | Description                                                    |  |  |

|-------------|----------------|----------|--------------|----------------------------------------------------------------|--|--|

| MFP         | 35             | DI       | VBAT         | Multi-function pin and software configurable as a reset input. |  |  |

## 1.4.5 Power supply device terminal functions

Table 1-8 QCC711 Power supply device terminal functions

| Signal name | Lead<br>number | Pad type | Power domain | Description                                                                                                                                          |  |  |

|-------------|----------------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SMPS_LX     | 27             | AO       | -            | Inductor connection for the Buck SMPS.                                                                                                               |  |  |

| VDD_1V2     | 34             | Р        | -            | 1.2 V supply for internal PMU control circuit and 32.768 kHz XTAL. An external 470 nF decouple capacitor is recommended.                             |  |  |

| VDD_1V8_IN  | 2              | Р        | -            | Supply for 32 MHz XTAL and SAR ADC. Connect directly to VDD_1V8_OUT (Lead 29) using PCB trace.  An external 10 nF decouple capacitor is recommended. |  |  |

| VDD_1V8_OUT | 29             | Р        | -            | 1.8 V supply for 32 MHz XTAL and SAR ADC. An external 470 nF decouple capacitor is recommended.                                                      |  |  |

| VDD_BAT     | 28             | Р        | -            | Battery voltage input. Two 0603-size external 10 μF capacitors are recommended.                                                                      |  |  |

| VDD_DIG     | 31             | Р        | -            | 1.1 V supply for digits core power. An external 470 nF decouple capacitor is recommended.                                                            |  |  |

| VDD_LA      | 30             | Р        | -            | 1.35 V supply to the system. A 0603-size external 10 μF decouple capacitor is recommended.                                                           |  |  |

| VDD_PA_IN   | 5              | Р        | -            | Supply for Bluetooth power amplifier. Connect directly to VDD_PA_OUT (Lead 32) using PCB trace. An external 10 nF decouple capacitor is recommended. |  |  |

| VDD_PA_OUT  | 32             | Р        | -            | 1.15 V supply for Bluetooth power amplifier. An external 470 nF decouple capacitor is recommended.                                                   |  |  |

| VDD_PADS_1  | 45             | Р        | -            | Power domain for PIO [8:0]. An external 100 nF decouple capacitor is recommended.                                                                    |  |  |

| VDD_PADS_2  | 8, 13, 26      | Р        | -            | Power domain for PIO [25:9]. An external 100 nF decouple capacitor is recommended for each lead.                                                     |  |  |

| VDD_RF_IN   | 3              | Р        | -            | Supply for Bluetooth radio. Connect directly to VDD_RF_OUT (Lead 33) using PCB trace. An external 10 nF decouple capacitor is recommended.           |  |  |

| VDD_RF_OUT  | 33             | Р        | -            | 1.1 V supply for Bluetooth radio. An external 470 nF decouple capacitor is recommended                                                               |  |  |

#### 1.4.6 Ground device terminal functions

Table 1-9 QCC711 Ground device terminal functions

| Signal name | Lead<br>number       | Pad type | Power domain | Description |  |

|-------------|----------------------|----------|--------------|-------------|--|

| VSS         | 25, Ground<br>Paddle | GND      | -            | Ground.     |  |

## 1.5 QCC711 PCB design and assembly considerations

Recommendations to achieve maximum board-level reliability of the QCC711 IC package.

Use of nonsolder mask defined (NSMD) lands (lands smaller than the solder mask aperture) are preferred because of the greater accuracy of the metal definition process compared to the solder mask process. With solder mask defined pads, the overlap of the solder mask on the land creates a step in the solder at the land interface, which can cause stress concentration and act as a point for crack initiation.

- Qualcomm Technologies International, Ltd. (QTIL) recommends that the printed circuit board (PCB) land pattern is in accordance with Institute of Printed Circuits (IPC) standard IPC-7351B.

- Solder paste must be used during the assembly process.

For more information about QCC711 PCB design, see QCC711 Hardware Design Guide (80-WL711-5).

## 1.5.1 Typical solder reflow profile

For further information describing the reflow profile of an integrated circuit (IC) when attaching its physical connection solder points to a PCB see *Typical Solder Reflow Profile for Lead-free Devices Information Note* (80-CT462-1).

## 1.6 Moisture sensitivity level

QCC711 is qualified to moisture sensitivity (MSL3) in accordance with JEDEC J-STD-020.

# 2 Bluetooth subsystem

The Bluetooth subsystem is a single-mode radio supporting Bluetooth Low Energy.

The Bluetooth subsystem is fully qualified to the Bluetooth v5.4 specification. It has:

- 32 MHz Arm Ltd. (Arm) Cortex-M0 processor running Bluetooth firmware

- Bluetooth packet processing engine and modem

- Power and clocks automatically removed to reduce power when the Bluetooth radio is not operating

## 2.1 Bluetooth v5.4

QCC711 supports Bluetooth Low Energy to the Bluetooth v5.4 specification.

## 2.2 Bluetooth radio

The Bluetooth radio consists of a single radio frequency (RF) input/output (I/O) port shared for receive and transmit. The RF port impedance is  $50 \Omega$  when operating.

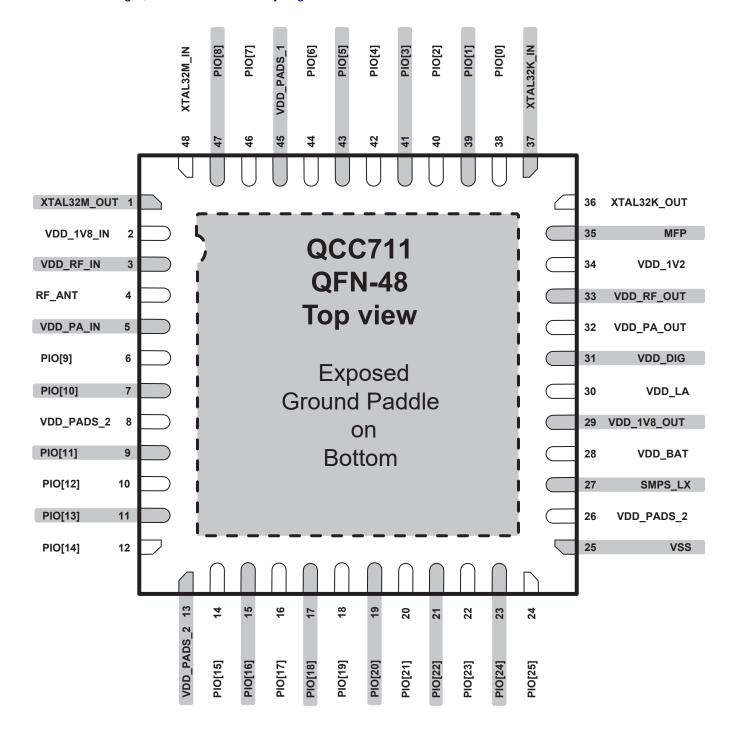

Figure 3-1 Crystal oscillator

The Bluetooth specification requires frequency accuracy of  $\pm 40$  ppm. The output RF frequency is directly linked to the frequency accuracy of the crystal oscillator, so this must be  $\pm 40$  ppm. This specification is required over the operating temperature of the device.

**NOTE** The crystal is specified by the following terms:

- Initial Frequency Error: The difference between the required frequency and the actual oscillating frequency caused by the crystal and its PCB connections. It is also called Calibration Tolerance or Frequency Tolerance

- Frequency Stability Error: The total of how far the crystal can move off frequency with temperature, aging, or other effects. It is also called Temperature Stability, Frequency Stability, or Aging.

- Pullability: The change in frequency for a change in load capacitance.

QCC711 contains an array of internal capacitors attachable to the XTAL\_IN and XTAL\_OUT nodes. These can be switched to pull the crystal onto frequency and compensate for initial frequency errors by using a simple per-device trim on the production line. The trim is stored in the Application subsystem. It is not possible to compensate for frequency stability errors. A crystal should be chosen with a frequency stability error better than the Bluetooth specification ±40 ppm clock accuracy.

Some crystal data sheets combine both these terms into one tolerance value. This results in compensation of only the initial frequency error and a trim that does not compensate for temperature or aging performance. If frequency stability is not explicitly stated, QTIL cannot guarantee remaining within the Bluetooth's ±40 ppm frequency accuracy specification.

The sum of Initial Frequency Error and Frequency Stability Error must be kept below the Bluetooth specification of ±40 ppm. Typically use a crystal with ±15 ppm frequency stability over temperature/aging.

To improve startup time and achieve minimum current consumption, crystals with low capacitive loading are preferred. However, this may result in greater susceptibility to environmental frequency variation.

#### 3.1 LPO CAL

LPO CAL is used to measure the frequency of another clock relative to a 32 MHz crystal. The control logic starts a counter running on a fast, accurate clock domain, and counts over a programmed number of edges of the target clock. Countval is divided by the number of edges over which the measurement is taken.

Measurement accuracy:

- Slow Clock: Using the fast clock to measure the slow clock introduces an error at the start and end of the measurement. With a slow edge counter of 800 every clock from ideal, can be shown to equate to 1.25 ppm of inaccuracy.

- Fast Clock: To measure a fast clock, it is necessary to scale the clock to ensure that no edges are missed when the edge count is taken. Therefore the measured clock is prescaled first. Over L clocks we can show the resolution ppm to be:

Resolution = (ClkMes / Scaling) / Counter x 32 MHz

## 3.2 32.768 kHz crystal

The QCC711 32.768 kHz crystal oscillator is used for:

- accurate wake up

- Bluetooth Low Energy sleep clock

A low power 32 kHz crystal oscillator is needed for timing in sleep modes. Matching load capacitances are provided on chip that support tuning of crystals requiring matching load capacitance from 4 pF to 12.5 pF. Lower current consumption is achieved with a smaller load capacitance crystal.

The system requires trimming to (32.768 kHz) better than 4 ppm with the onboard adjustable load capacitance (oscillator, an array of internal capacitors attachable to the XTAL\_IN and XTAL\_OUT nodes, 35 fF effective steps) and compensated for initial frequency errors using a simple per-device trim on the production line at room temperature.

Frequency pullability depends on the matching load capacitance of the crystal. Current consumption also depends on the equivalent series resistance (ESR) of the crystal – a smaller ESR gives lower consumption.

At the same time as the frequency trim, the crystal type (setting based on load cap and ESRmax) must be loaded to resistive random-access memory (RRAM), to ensure correct operation, and minimize operating current; before running the crystal. Parasitic capacitance on the PCB to the crystal must be minimized to allow tuning of the crystal (particularly for small load capacitance crystals). It must be below 3 pF per terminal for 4 pF crystals, and 4 pF per terminal for 6 pF and larger crystals. Of this capacitance, less than 0.2 pF may be shunt capacitance (between XTAL\_IN and XTAL\_OUT).

## 3.3 32 MHz crystal

The QCC711 32 MHz crystal oscillator is used for:

- RF activity

- UART baud clock

- for running applications when Bluetooth Low Energy is not awake

Any of the three subsystems can request the use of the 32 MHz crystal oscillator as the high frequency clock source; this is as opposed to the alternate, lower accuracy internal high frequency low-power oscillator (HFLPO).

This crystal oscillator is automatically powered off and deselected when the system on-chip (SoC) goes into Sleep or Hibernate state, at which time the SoC switches to its internal low frequency low-power oscillator (LFLPO). Both the oscillator choice and the configuration of the oscillator, persist across low power states, and are automatically restored when the SoC wakes up into Active state.

The management of the oscillator is automated and software is relieved of most monitoring tasks. Ordinarily, software only needs to select a clock source and the hardware manages all other items of concern.

### 3.4 Global clock controller

The global clock controller (GCC) is responsible for clock and reset distribution for different subsystems. Clock gates are inserted in front of each subsystem, to gate the clock off near clock origin, and to reduce dynamic power consumption whenever the subsystem is not needed.

The GCC has an internal hardware finite state machine (FSM) that triggers the start-up sequence for the 32 MHz crystal when requested, after exiting from QCC711 Sleep state.

#### **3.4.1** Timers

A 44-bit global timer and a 32-bit central timer (with capture and compare capabilities) are available. The global timer provides 1 µs resolution at 16 MHz (effective update rate).

The central timer block provides 12 different microsecond resolution comparators that can be mapped to any of the interrupt lines to the Applications subsystem. Hardware can detect when firmware is late (within a certain time) when programming a compare value, and generating a corresponding interrupt. The actual time is captured in memory mapped registers. A closest-in-time circuit provides information on which enabled comparator matches next.

Configurable timer capture mechanisms are provided to capture certain external trigger or internal firmware events.

## 3.5 32.768 kHz crystal performance specification

Table 3-1 lists 32.768 kHz crystal performance specification for QCC711.

**NOTE** Performance to be met over operating temperature range unless otherwise stated.

Table 3-1 QCC711 32.768 kHz crystal specification

| Parameter                    | Min   | Тур    | Max        | Units               | Notes       |

|------------------------------|-------|--------|------------|---------------------|-------------|

| Operating frequency          | -     | 32.768 | -          | kHz                 | -           |

| Mode of Vibration            |       | ı      | Fundamenta | AT-cut fundamental. |             |

| Initial frequency tolerance  | -20   | -      | 20         | ppm                 | 25°C ± 3°C. |

| Turnover                     | 20    | 25     | 30         | °C                  | -           |

| Parabolic coefficient        | -0.04 | -      | -          | ppm/°C <sup>2</sup> | -           |

| Aging                        | -     | -      | 3          | ppm/year            | -           |

| Operating temperature        | -40   | -      | 85         | °C                  | -           |

| Storage temperature          | -40   | -      | 125        | °C                  | -           |

| Equivalent series resistance | -     | -      | 90         | kΩ                  | -           |

| Motional capacitance         | 0.6   | -      | 10         | fF                  | -           |

| Shunt capacitance            | -     | -      | 1.5        | pF                  | -           |

| Load capacitance             | 4     | -      | 12.5       | pF                  | -           |

| Drive Level                  | -     | -      | 1          | μW                  | -           |

| Insulation resistance        | 500   |        | -          | MΩ (100 V)          | -           |

## 3.6 32.768 kHz crystal selection considerations

Best power consumption is obtained by using a crystal with the lowest possible matching load capacitance and ESR. This permits a lower drive level setting of the driver circuit. The expectation is that changing from a typical 6 pF to 4 pF load capacitance crystal, could save approximately 28 nA in Sleep state. Optimal power consumption is obtained with a crystal with a 4 pF capacitance load.

## 3.7 32 MHz crystal performance specification

Table 3-2 lists performance to be met over operating temperature range unless otherwise stated.

Table 3-2 Electrical requirements

| Parameter         | Description                                        | Min | Тур | Max | Units  | Notes                                                                       |

|-------------------|----------------------------------------------------|-----|-----|-----|--------|-----------------------------------------------------------------------------|

| F <sub>nom</sub>  | Nominal<br>fundamental<br>frequency                | -   | 32  | -   | MHz    | -                                                                           |

| СР                | Package<br>capacitance<br>(32 MHz)                 | -   | 1   | 2   | pF     | -                                                                           |

| C <sub>L</sub>    | Load capacitance                                   | -   | 6   | 10  | pF     | -                                                                           |

| F_tol_nom         | Frequency tolerance nominal                        | -10 | -   | 10  | ppm    | At 25°C ± 3°C                                                               |

| F_tol_temp        | Frequency stability over temperature               | -10 | -   | 10  | ppm    | Over specified temperature range with respect to frequency error at nominal |

| F_tol_aging       | Frequency tolerance with aging at Ta = 25°C ± 3°C  | -1  | -   | 1   | ppm/yr | 1 <sup>st</sup> year                                                        |

| F_tol_aging_10yrs | Total frequency tolerance with aging over 10 years | -10 | -   | 10  | ppm    | -                                                                           |

| ESR               | Motional Resistance<br>(32 MHz)                    | -   | 25  | 50  | Ω      | -                                                                           |

| Drive Level       | DL                                                 | -   | 100 | 200 | μW     | -                                                                           |

## 3.8 32 MHz crystal selection considerations

To meet the Bluetooth specification, it is important that the frequency tolerance of the 32 MHz clock stays within ±40 ppm for the lifetime of the product. A customer should remove initial frequency error at production test, by adjusting load capacitors. Load capacitor adjustment removes error introduced by the crystal, assembly, and parasitics; particularly for board and chip pin. Remaining tolerance should be provided to handle the effects of temperature and aging.

# 4 System power states

The Always ON (AON) module provides the minimum digital functionality required to remain operational in the lowest power modes, as well as a number of not-always-on (NAON) functions. The power management engine (PME) provides always-on control of device boot and provides control of power state, clocks and resets, and memory retention based on requests from firmware.

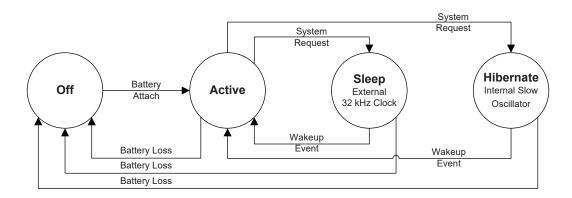

Figure 4-1 shows QCC711 power states.

Figure 4-1 QCC711 power states diagram

In Off state the SoC is not powered. The lowest power consumption state is Hibernate, followed by Sleep and then Active.

The SoC can automatically adjusting its power state with minimum intervention from subsystem software. The SoC automatically moves into its lowest power consumption state, consistent with subsystem requirements, as expressed by the subsystem software through a set of voting registers.

#### 4.1 Off state

In Off state, no battery is attached, and QCC711 is inert. When a battery is attached, QCC711 transitions to Active state automatically.

#### 4.2 Active state

In Active state, the main power domain is powered on and subsystems can operate normally.

In Active state, the chip runs subsystem software as determined by the configuration requested by software. In the most common case of an operative chip, in this state, the SoC runs software on one or more of its three subsystems. As soon as all three subsystems request to be put in low power mode, the SoC as a whole transitions into Sleep or Hibernate state, depending on software preference.

## 4.3 Sleep state

In Sleep state most of the SoC is powered off. The SoC remains capable of waking up into Active state under a number of conditions.

If enabled the 32 kHz crystal remains running and continues to be used as the time reference clock.

oti1593441908917.3

In particular, it is possible to program an accurate wake-up time for the Applications and/or the Bluetooth subsystem, with precisions compatible with the timing needs of Bluetooth protocols.

In Sleep state the SoC tracks real time.

## 4.4 Hibernate state

In Hibernate state the SoC powers down as much logic as possible while still retaining a certain amount of configuration and the capability to wake up.

In this state, timed wake-ups can be programmed as in Sleep state but with far lower accuracy. And the SoC loses the ability to track real time with usable accuracy.

# 5 Applications subsystem

The QCC711 Applications subsystem provides a processor and resources for customer application code execution.

## 5.1 Application subsystem features

The QCC711 Application subsystem features:

- a 32 MHz Arm Cortex-M3 processor for customer execution that features memory protection logic and can

execute code with or without a real-time operating system (RTOS)

- non-volatile memory (NVM) for program storage, using on-chip RRAM

- peripheral interface control of universal asynchronous receiver transmitter (UART), inter-integrated circuit interface (I<sup>2</sup>C), and serial peripheral interface (SPI)

- bit-banding access to top-level mode multiplexing (TLMM) registers

- Arm CoreSight debugger support

- 4-bit trace port and single wire output (SWO) support

- address remapping for NVM and static random access memory (SRAM) boot support

- boot address offset support within NVM and SRAM regions

- Sleep and Power-down modes support

## **6** SRAM module

The SRAM module provides a pool of SRAM memory shared between Bluetooth (M0), Applications (M3), and Root of Trust subsystem processors. Memory allocation is flexible and runtime configurable.

QCC711 has a total of 128 KB of SRAM for these subsystems. This memory is configured as 16 memory blocks of 8 KB each:

- 32 KB for retention support

- remaining 96 KB is power collapsed in QCC711 Sleep state

Up to 64 KB (of the 128 KB) is available for customer applications:

- 16 KB for retention support

- 8 KB shared between M0 and M3

- 40 KB for any use with repartition between shared and customer specific usage (adjustable in blocks of 8 KB)

## **7** NVM module

The NVM module provides 512 KB of shared RRAM memory to the system.

The NVM presents a memory divided into regions, to support multiple subsystems. The NVM module uses an embedded 4 Mb RRAM.

Memory is divided into 16 regions, with each region having its own access control settings. These regions are under Qualcomm or customer control.

The NVM is a single resource, with multiple subsystems accessing it. The Root of Trust (RoT) subsystem is the owner of the NVM and configures it by setting region allocation and access control. When the NVM is configured, subsystems have read access to their respective memory regions. The RoT does not need to manage read access from the subsystems. When a subsystem wants to write to a memory region, the RoT allocates NVM module functions to the subsystem, and the subsystem writes to the memory. The subsystem can manage its own access control to the allocated memory regions.

The 512 KB of shared RRAM memory is allocated:

- 64 KB for M0

- 64 KB for RoT

- 384 KB for customer applications

NOTE This 384 KB is for both code and data; in particular data for OTA-U (as required).

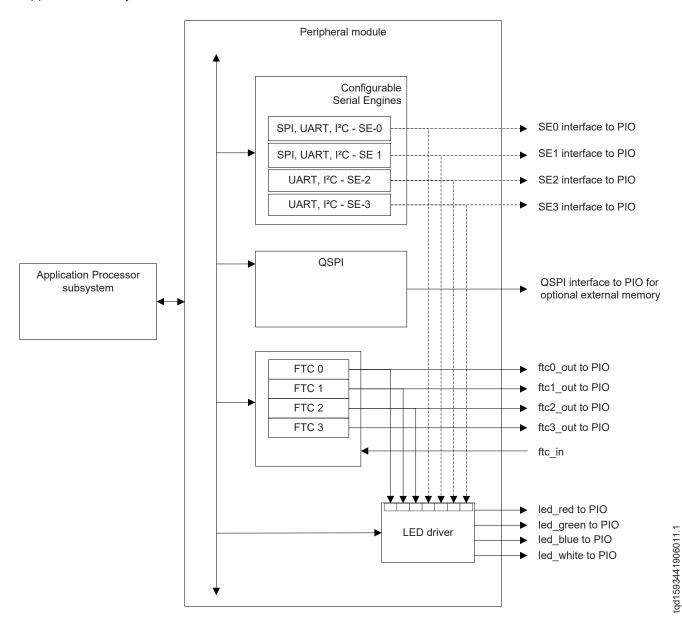

# 8 Peripheral module

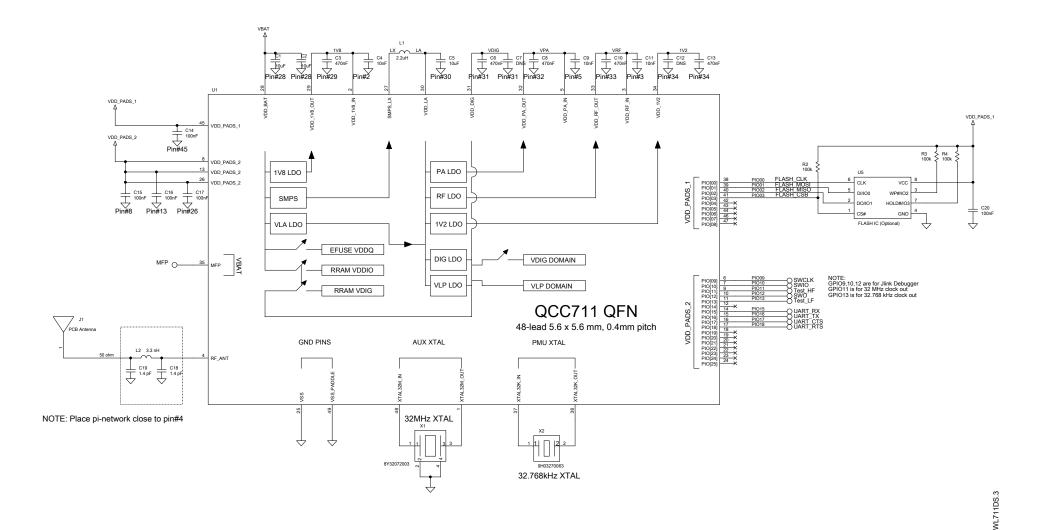

Figure 8-1 shows the QCC711 peripheral module.

The primary purpose of the Peripheral module is to provide interfaces for customer application use and control from the Applications subsystem.

Figure 8-1 QCC711 Peripheral module

## 8.1 Peripheral module features

The QCC711 Peripheral module incorporates different controller and peripheral intellectual property (IP)s for certain use cases. It includes integrated direct memory access (DMA) that supports both transfers to and from peripheral interfaces, and memory-to-memory transfers. Table 8-1 lists the peripherals available for QCC711.

Table 8-1 QCC711 peripheral IPs

| Components                        | High-level specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSPI controller                   | <ul> <li>used for external flash</li> <li>configurable controller and peripheral SPI</li> <li>4-wire/8-bit standard interface</li> <li>slower clock rate operation support</li> <li>dual/quad SPI support</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FTC                               | <ul> <li>application timer and light-emitting diode (LED) pattern driving capability supported</li> <li>up to 4 timer/counter instantiations</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LED pattern generator             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SEs / QUPs offer the following ca | pabilities:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3 x UART                          | <ul> <li>up to 2 Mbaud maximum UART rate capability</li> <li>8-bit and 9-bit mode</li> <li>2x UARTs support 9-bit data transfer mode</li> <li>hardware flow control</li> <li>DMA to / from system memory to reduce first-in first-out (FIFO) size and processor load</li> <li>programmable fractional baud rate generation from 32 MHz system clock</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2 x I <sup>2</sup> C controllers  | <ul> <li>controller SM, FM, and FM+ external pull-up resistors</li> <li>100 kbps, 400 kbps, and 1000 kbps rates</li> <li>external pull-up resistors required</li> <li>DMA to/from system memory to reduce FIFO size and processor load</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPI controllers                   | <ul> <li>configurable 3-wire / 9-bit mode and 4-wire / 8-bit mode</li> <li>compatible with SPI-based display/sensor interfaces</li> <li>slower clock rate operation supported</li> <li>3-wire and 4-wire SPI for display supported by serial engine (SE) 0</li> <li>true 4-wire SPI</li> <li>capable of concurrent operation, with DMA support</li> <li>clock divider for lower frequency operation with limited capability devices</li> <li>4-wire 8-bit controller mode for external flash, other SPI-based displays/sensors, and standard peripherals</li> <li>4-wire 8-bit SPI peripheral mode</li> <li>32-bit mode with DMA, for arbitrary pattern generation from memory under application firmware control - output of this SPI mode may be connected to FTC inputs for extra</li> </ul> |

| DMA                               | application flexibility to drive LED patterns  ■ date size: 8-bit, 16-bit, and 32-bit supported  ■ DMA transfer types between memories and peripherals supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## 8.2 QSPI controller

The QCC711 quad serial peripheral interface (QSPI) controller:

- supports dual/quad SPI mode for higher performance data transfer capability

- execution in place is not supported on this interface

## 8.3 Flexible timer/counter

The QCC711 has four flexible timer/counter (FTC) blocks, this is a common function that is found in almost all mixed signal microcontrollers.

Each FTC block has the following main features:

- application timer and LED pattern driving capability with up to four timer/counter instantiations

- support for LED pattern-flashing

- 16-bit counter/timer

- various operating modes:

- count up, down or up-down

- single shot or continuous

- free running from clock source or gated

- edge, signed, and triggered count modes

- configurable clock sources:

- internal clock

- external clock from a pad with optional gating, clocked on rising, falling or both edges

- count on multiple input clocks (for quadrature encoder behavior)

- cascaded from another FTC block for longer than 16-bit counters

- 16-bit programmable counter clock prescaler

- auto-reload register (counter maximum value)

- 3 capture/compare channels (configurable as input capture or compare/pulse width modulation (PWM))

- configurable noise filter on inputs

- flexible counter event control, enabling the following input measurement/capture functions:

- clock period measurement

- pulse width measurement

- quadrature decoder (X1, X2, X4 decoding types)

- the preceding functions are achieved through the following counter event control features:

- start, stop, increment, decrement, and clear events individually triggerable by:

- register write

- programmable input/output (PIO)

- overflow of previous cascaded FTC block

- event edge detection:

- rising edge

- · falling edge

- · either edge

- neither edge (disabled)

- multiple output waveform generators, enabling complex output waveform generation:

- multiple PWM outputs with optional dead time between outputs for driving motor bridges

- variable frequency generation

- the preceding functions are achieved through the following output generation control features:

- match with comparator/s, maximum value reached, zero value reached, and manually triggered events that control the output behavior as follows:

- toggle output

- · set output high

- reset output low

- unchanged (disabled)

- interrupt generation on the following events:

- counter overflow/underflow

- input capture

- capture overflow

- compare match

- trigger event (counter start / stop / init by internal / external trigger)

- programmable operation during debug mode

### 8.4 QCC711 serial engines and supported interfaces

QCC711 has four programmable SE / Qualcomm universal peripheral (QUP) that are configurable for serial interfaces, such as SPI, UART, or I<sup>2</sup>C, see Table 8-2.

Table 8-2 QCC711 serial engines and supported interfaces

| SE/QUP | 3-wire or 4-<br>wire SPI<br>display<br>controller | True 4-wire SPI<br>controller/<br>peripheral | I <sup>2</sup> C controller | UART | 9-bit UART | DMA |

|--------|---------------------------------------------------|----------------------------------------------|-----------------------------|------|------------|-----|

| SE0    | Yes                                               | Yes                                          | Yes                         | Yes  | Yes        | Yes |

| SE1    | Yes                                               | Yes                                          | Yes                         | Yes  | Yes        | Yes |

| SE2    | No                                                | No                                           | Yes                         | Yes  | No         | Yes |

| SE3    | No                                                | No                                           | Yes                         | Yes  | No         | Yes |

Each SE has five output ports. The functions of these ports are specific to each of the selected interfaces. Table 8-3 lists the port feature mapping. The following section shows how these ports can be routed as sets to different physical PIOs. As such, the ports of each SE are presented as numerous copies to the top level multiplex. Alternative copies must be used as a complete block, this restriction keeps the physical interface grouped to adjacent PIOs.

The SEs that Table 8-3 lists have default port mappings for the different types of interface, see Table 8-3.

Table 8-3 Default port mappings for QCC711 serial engines

| Default SE port mapping | 3-wire SPI display | 4-wire SPI display | I <sup>2</sup> C | UART | SE0 true 4-wire<br>SPI |

|-------------------------|--------------------|--------------------|------------------|------|------------------------|

| Port 0                  | CS1                | CS1                | SDA              | CTS  | MISO                   |

| Port 1                  | SDIN               | SDIN               | SCL              | RFR  | MOSI                   |

| Port 2                  | CLK                | CLK                | -                | TX   | CLK                    |

| Port 3                  | cs                 | cs                 | -                | RX   | cs                     |

| Port 4                  | -                  | D/C                | -                | -    | CS1                    |

QCC711 serial engine ports in Table 8-3 can be mapped to specific PIOs, see *Related Information*.

RELATED INFORMATION

"PIO" on page 40

#### 8.4.1 UART

QCC711 has the following UART features:

- 3 x UARTs

- up to 2 Mbaud maximum UART rate capability

- hardware flow control

- programmable fractional baud rate generation from 32 MHz system clock

- DMA to and from system memory to reduce FIFO size and processor load

- 2 x UARTs supporting 9-bit data transfer mode

QCC711 has a standard UART serial interface that provides a simple mechanism to communicate with other serial devices using the RS232 protocol. The UART interface multiplexes with PIOs and other functions. Hardware flow control is optional. Table 8-4 lists possible UART settings.

Table 8-4 UART configuration options

| Pa                                            | ırameter | Possible value     |  |

|-----------------------------------------------|----------|--------------------|--|

| Baud rate                                     | Minimum  | 2400 (≤1%Error)    |  |

|                                               | Maximum  | 2 MBd (≤1%Error)   |  |

| Flow control                                  |          | RTS/CTS or None    |  |

| Parity                                        |          | None, Odd, or Even |  |

| Number of stop bits                           |          | 1 or 2             |  |

| Bits per byte (Applies to all Serial Engines) |          | 8                  |  |

| Bits per byte (Applies to SE0 and SE1         |          | 9                  |  |

Table 8-5 lists supported baud rates and the QCC711 percentage error for that rate.

Table 8-5 Supported UART baud rates

| Supported UART baud rate | Error (%) <sup>a</sup> |

|--------------------------|------------------------|

| 2400                     | 0.04                   |

| 4800                     | 0.16                   |

| 9600                     | 0.16                   |

| 19200                    | 0.16                   |

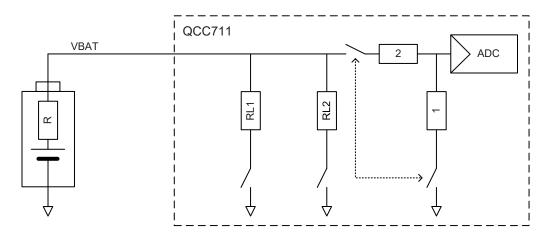

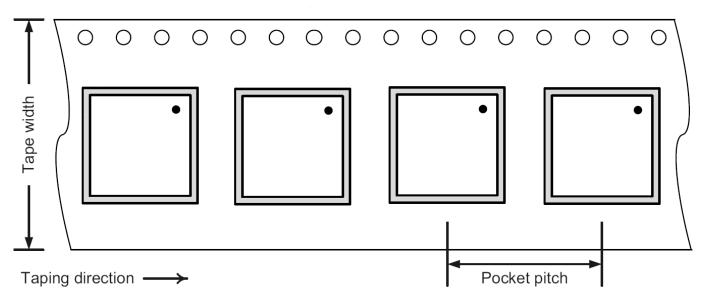

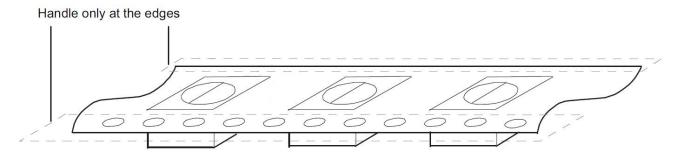

| 38400                    | 0.16                   |